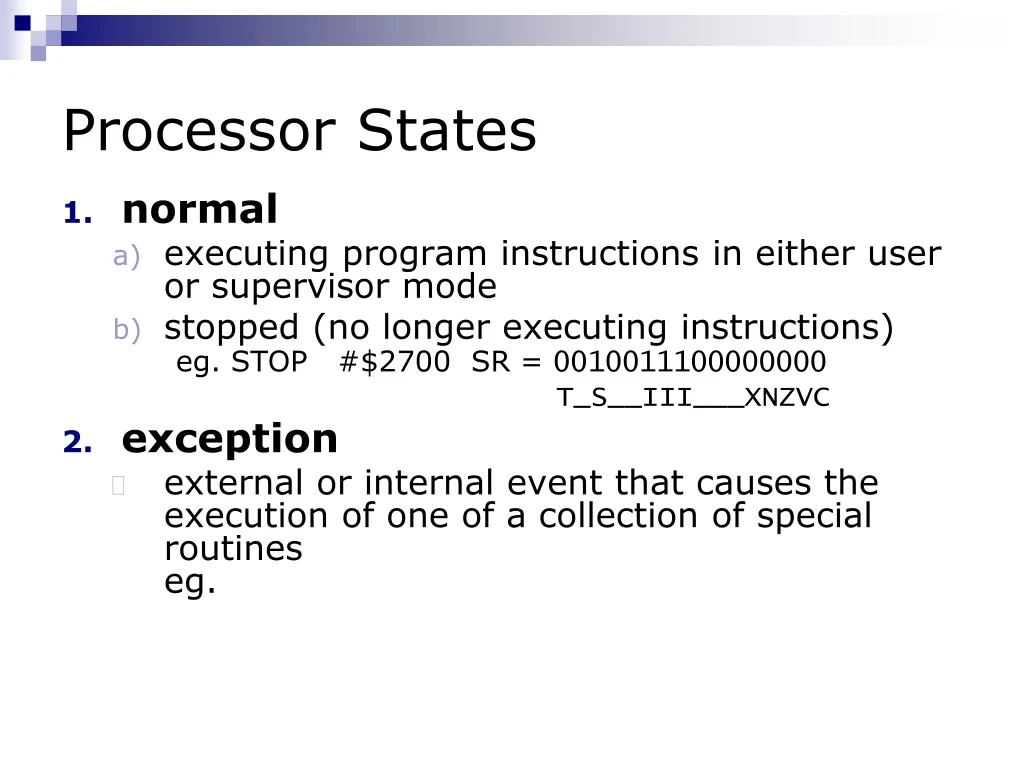

Processor States

E N D

Presentation Transcript

Processor States • normal • executing program instructions in either user or supervisor mode • stopped (no longer executing instructions)eg. STOP #$2700 SR = 0010011100000000 T_S__III___XNZVC • exception • external or internal event that causes the execution of one of a collection of special routineseg.

Processor States • halted • indicates system error condition • system cannot reliably continue execution • requires externally generated reset to restart e.g. address exception error • program attempts to access a word or longword at an odd address e.g. bus error exception • program attempts to address a nonexistent memory location

Exceptions/Interrupts • Hardware Interrupt (aka interrupts) • external signal applied to interrupt pins • on 68000, pins IPL2, IPL1, IPL0 • when will the interrupt occur? • on EASy68K, • handled by EASy68 K (default) ; you have to enable “exception processing” to take over control • simulated via pushbuttons • caused by mouse, keyboard

Exceptions/Interrupts • Conditional Interrupt (aka exception) • the condition is produced by the execution of an instruction e.g. executing DIVS or DIVU → if the divisor is zero • when will the interrupt occur?

Exceptions/Interrupts • Software Interrupt (aka trap) • under program control, i.e. an explicit call e.g. TRAP #15 • when will the interrupt occur?

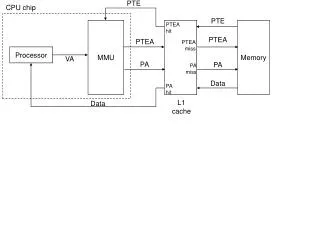

Terminology interrupt / exception / trap • action that initiates a special service routine • range of interrupt types depends on the microprocessor service routine / interrupt routine / interrupt handler / trap routine / exception handler / interrupt service routine (ISR) • routine (similar to subroutine) that services or handles the interrupt exception sequence • handling actions that occur when an interrupt happens • set by the microprocessor hardware designer and executed by the hardware exception vector --> $0 to $3FF in 68000 • area of memory starting at address 0 that directs handling to the ISR • exception vectors always start at address 0 • exception vector length depends on the range of interrupts that the microprocessor handles • entries in the exception vector contain either an address (e.g. 68000) or an instruction (e.g. PIC micros, goto instruction)

Calculating the ISR Address • determined from the vector table For example, level 1 hardware interrupt 1. locate the interrupt on the vector table

Calculating the ISR Address 2. interrupt will have a vector number 3. multiply the vector number by 4 to generate the vector address e.g. level 1 hardware interrupt vector # vector address 4. place the address of the ISR at the vector address

e.g. turn off all LEDs when level 1 interrupt pressed (EASy68K)

e.g. turn off all LEDs when level 1 interrupt pressed (EASy68K) LEDS equ $E00010 org $1000start end start What would happen if level 2 interrupt pressed?

Reading/Expectations: Reading: • Table 6-2. Exception Vector Assignment from page 6-7 of M68000 8-/16-/32-Bit Microprocessors User’s Manual [pdf, 184 p; Motorola] • The above table provides the vector number and vector address in both hexadecimal and decimal. Many tables only provide the vector number in decimal and you would have do the required conversions and calculations. Normally, the vector address is programmed in hexadecimal. • Add this table (was handed out in class) to your reference material. Bring it to the exam. Expectations: • you will be able to write an ISR for a hardware interrupt, for a conditional interrupt, and for a software interrupt • you will be able to explain how the interrupt sequence works