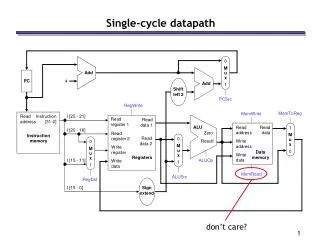

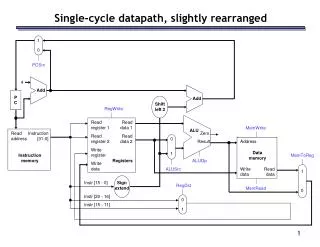

Single-cycle datapath

0 M u x 1. Add. PC. 4. Add. Shift left 2. PCSrc. RegWrite. MemToReg. MemWrite. Read address. Instruction [31-0]. I [25 - 21]. Read register 1. Read data 1. ALU. Read address. Read data. 1 M u x 0. I [20 - 16]. Zero. Read register 2. Instruction memory. Read

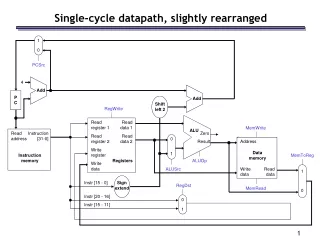

Single-cycle datapath

E N D

Presentation Transcript

0 M u x 1 Add PC 4 Add Shift left 2 PCSrc RegWrite MemToReg MemWrite Read address Instruction [31-0] I [25 - 21] Read register 1 Read data 1 ALU Read address Read data 1 M u x 0 I [20 - 16] Zero Read register 2 Instruction memory Read data 2 0 M u x 1 Result Write address 0 M u x 1 Write register Data memory Write data Registers I [15 - 11] ALUOp Write data MemRead ALUSrc RegDst I [15 - 0] Sign extend Single-cycle datapath don’t care?

R-type execution R-type writeback Op = R-type Instruction fetch and PC increment Branch completion Register fetch and branch computation Op = BEQ Memory write Effective address computation Op = SW Memory read Register write Op = LW/SW Op = LW FSM for multicycle control unit • Clock triggers transitions • #cycles = length of longest graph cycle

Executing a beq instruction • How many cycles? • Instruction fetch (memory) • PC increment by 4 (ALU) • Register fetch (register file) • Register comparison (ALU) • Branch target computation (ALU)

Executing a beq instruction • How many cycles? • Instruction fetch (memory) must be first • PC increment by 4 (ALU) • Register fetch (register file) • Register comparison (ALU) • Branch target computation (ALU)

Executing a beq instruction • How many cycles? • Instruction fetch (memory) must be first • PC increment by 4 (ALU) before next IF • Register fetch (register file) • Register comparison (ALU) • Branch target computation (ALU)

Executing a beq instruction • How many cycles? • Instruction fetch (memory) must be first • PC increment by 4 (ALU) merge into one • Register fetch (register file) • Register comparison (ALU) • Branch target computation (ALU)

Executing a beq instruction • How many cycles? • Instruction fetch (memory) must be first • PC increment by 4 (ALU) • Register fetch (register file) before comparison • Register comparison (ALU) • Branch target computation (ALU)

Executing a beq instruction • How many cycles? • Instruction fetch (memory) must be first • PC increment by 4 (ALU) • Register fetch (register file) before comparison • Register comparison (ALU) before finding target • Branch target computation (ALU)

Executing a beq instruction • How many cycles? • Instruction fetch (memory) must be first • PC increment by 4 (ALU) • Register fetch (register file) before comparison • Register comparison (ALU) before finding target • Branch target computation (ALU) so, must be last 4 cycles

Executing a beq instruction • How many cycles? • Instruction fetch (memory) must be first • PC increment by 4 (ALU) • Register fetch (register file) before comparison • Register comparison (ALU) before finding target • Branch target computation (ALU) so, must be last 4 cycles 3 cycles

Optimistic execution • Wasteful, bu no harm doing the computation early. • If the branch is not taken, we can just ignore the ALU result. • This idea is also used in more advanced CPU design techniques • branch prediction