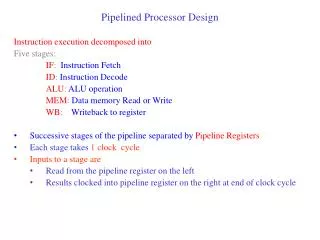

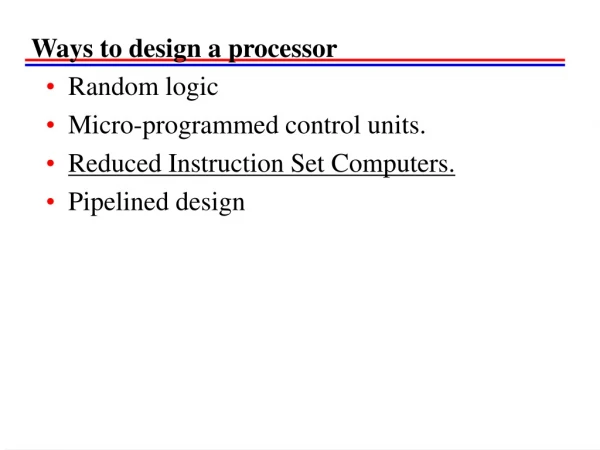

A Sea Change in Processor Design

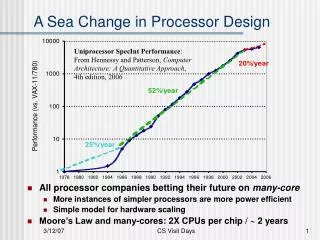

A Sea Change in Processor Design. Uniprocessor SpecInt Performance : From Hennessy and Patterson, Computer Architecture: A Quantitative Approach , 4th edition, 2006. All processor companies betting their future on many-core More instances of simpler processors are more power efficient

A Sea Change in Processor Design

E N D

Presentation Transcript

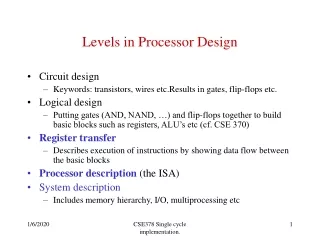

A Sea Change in Processor Design Uniprocessor SpecInt Performance: From Hennessy and Patterson, Computer Architecture: A Quantitative Approach, 4th edition, 2006 • All processor companies betting their future on many-core • More instances of simpler processors are more power efficient • Simple model for hardware scaling • Moore’s Law and many-cores: 2X CPUs per chip / ~ 2 years CS Visit Days

Research Accelerator for Multiple Processors Problem with Sea Change: • Compilers, operating systems, architectures not ready for 1000s of CPU per chip • How do we do research on 1000 CPU systems in arch., OS, compilers, OS, apps? Solution: • Create flexible (parameterized) 1000 CPU system from 10’s of FPGAs • Distribute out-of-the-box Massively Parallel Processor that runs standard binaries & OS • First system based on BEE2 (Berkeley Emulation Engine) - FPGA reconfigurable computing platform. • RAMP Description Language (RDL) defines and supports standard module interfaces and execution model. Used to describe “plumbing” to connect “gateware” units. CS Visit Days

Message passing machine MPI, UPC, Clusters 8 BEE2 modules, all-to-all connectivity over 10Gps links. Configuration, debugging, etc. over 100Mbps Enet. Initial applications: UPC NAS Parallel Benchmarks. 4 user FPGAs on each module hold 100MHz Xilinx MicroBlaze soft cores running UCLinux. Currently 8 cores per FPGA, 256 cores total. Each FPGA holds a packet network switch, shared memory controller, shared DP FPU, shared “console” switch RAMP Blue CS Visit Days

Computer Architecture & Engineering Core Faculty: David Culler, Kurt Keutzer, John Kubiatowicz, Dave Patterson, John Wawrzynek, Krste Asanovic (defecting from MIT Fall’07) Others active in computer architecture research: Demmel, Kahan, Katz, Nikolic, Rabaey, Smith, Yelick Topics Covered: ManyCore Parallel Architectures and Systems Emulation of Highly Parallel Systems Self aware computing systems Low-power system design Reconfigurable computing Architectures for novel substrates CS Visit Days