Help with Processor Stages

Get help with processor stages, diagrams, text, and audio descriptions for MIPS assembly instructions and register formats.

Help with Processor Stages

E N D

Presentation Transcript

Help with Processor Stages Diagrams, text and audio descriptions

MIPS Assembly Instructions REGISTER (R) FORMAT INSTRUCTIONS: add $t2,$t3,$t4 # add sll $s3,$t2,18 # shift left logical slt $t1,$s3,$s4 # set less than IMMEDIATE (I) FORMAT INSTRUCTIONS lw $t1,count # load word addi $s3,$s2,4 # add immediate bne $t0,$t1,label # branch not equal JUMP (J) FORMAT INSTRUCTIONS jal Xroutine # jump and link

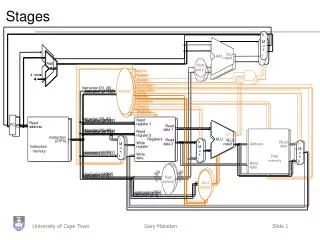

Vocabulary • PC: Program Counter: Address of next instruction to be executed • IR: Instruction Register: Register holding the instruction being executed • ALU: Arithmetic Logic Unit: That unit that performs arithmetic and logic operations (e.g., add, compare, shift, multiply, etc.) • SE: Sign Extend: Extend the arithmetic sign (+/-) from a 16-bit register to a 32-bit register • Register File: The 32 registers are held here. • Instruction cache: Fast memory that holds instructions • Data cache: Fast memory that holds data (for lw, sw)

Processing an Instruction Example: add $t1,$t2,$t3 • Fetch the instruction from memory; put into instruction register • Increment the Program Counter (PC) to point to the next instruction • Fetch the $t2 and $t3 registers from the register file. • Add the $t2 and $t3 registers in the Arithmetic Logic Unit (ALU) putting the result in the ALU out register (ALUOut) • Store the ALUOut register into the $t1 register in the register file.

Processing an Instruction Example: sw $t1, 25($t3) • Fetch the instruction from memory; put into instruction register • Increment the Program Counter (PC) to point to the next instruction • Fetch the $t1 and $t3 registers from the register file. • Sign extend the immediate 25 from the Instruction Register • Add the 25 and $t3 registers in the Arithmetic Logic Unit (ALU) putting the result in the ALU out register (ALUOut) • Write to memory the contents of the $t1 register to the address provided by the ALUOut.

Instruction Fetch Always Done: PC <= PC + 4 IR <= InstrCache[PC] PC <=PC+4 IR

Instruction Decode & Register Read These steps are always done: RS <= RegFile[IR[25:21]]; RT <= RegFile[IR[20:16]]; Immediate <= sign-extend(IR[15:0]); pcALUOut <= PC + (Immediate << 2); For designs of specific instructions, you don’t need to show all paths (e.g. addi does not use RT or jta) rs rt multiplexer Sign-extend Immediate 16->32 bits Op Code & Function code

ALU Operation Instruction is specific to Instruction type: R-Type Instruction: ALUOut <= RS op RT I-Type Instruction: ALUOut <= RS op Immediate Memory-Reference Instr: ALUOut <= RS + Immediate Branch Instruction: If (RS/x compare RT/y) PC <= ALUOut Jump Instruction: PC <= (PC(31:28), (IR[25:0],2*b00))

Completion 1: Data Cache Access This stage is instruction-specific: R-Type Instruction: RegFile[IR[15:11]] <= ALUOut Memory-Reference Instr: Load Instr: DataCacheOut <= DataCache[ALUOut] Store Instr: DataCache[ALUOut] <=RT lw, sw: address sw only: data

Completion 2: Register Writeback Load Instr: RegFile[IR[20:16]] <= DataCacheOut R-type, Other I-types lw (load word) only

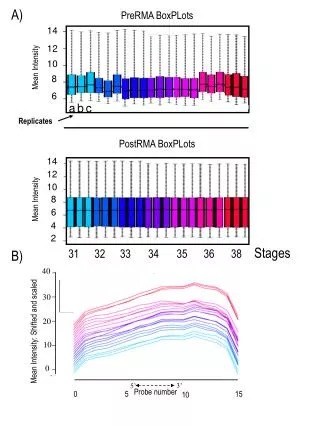

One Stage per Clock Cycle Instr Fetch Instruction Decode ALU Oper Cache Access Reg Writeback alu out ir rs rt rd