Nanoscale Structures in Integrated Circuits: Advancements and Challenges

190 likes | 266 Vues

Explore the evolution of chip manufacturing methods, limitations, and future possibilities including molecular chip making and germ-based circuits. Learn about Moore's Law, current lithography techniques, and innovative research progress.

Nanoscale Structures in Integrated Circuits: Advancements and Challenges

E N D

Presentation Transcript

Nanoscale structures in Integrated Circuits By Edward Mulimba

Presentation Outline • Introduction and history • Review of current chip manufacturing methods • Limitations of current methods • 2 currently researched methods • conclusion

Nanotech Definition • Creation and use of materials, systems or components involving measurements between 1 and 100 nm • nanometer = one billionth of a meter (10 –9 meter ) • Herald new advances in engineering, medicine, and computing • Spending US ($3.7 billion) Japan ($1 billion) and EU($3.3 billion)

What is Integrated Circuit? • Small electronic device made from semiconductor material (usually silicon) • Developed mainly by Jack Kilby of Texas Instruments • Usually contains transistors and other small components

Moore’s Law • Intel co founder Gordon Moore observed in 1965 • Number of transistors per integrated circuit chip would double in each technology generation • Early generation just had 30 transistors, today could exceed few hundred million per chip.

Table showing transistor size trend Source ITRS Executive Summary 2003 Edition

Current basic chip fabrication method LIGHT MASK PHOTORESIST FILM SUBSTRATE

Current lithography techniques • Extreme ultraviolet (EUV) lithography • Most prominent • Backed by Intel, Motorola, and now IBM • Uses very short wavelength

Current lithography techniques (cont) • Electron-beam lithography • Backed by Lucent Technology, Nikon • Uses electrons instead of light • Takes too long to make chip

Current lithography techniques (cont) • Maskless lithography • Developed jointly by Swedish and Dutch companies • Uses millions of microscopic mirrors to direct laser light on wafer • Too slow and costly

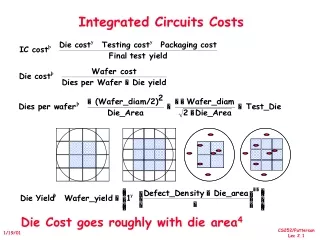

Limitations of current chip fabrication methods • Cost of fabrication plants is exorbitant • Moore’s second law – corollary to first “The cost of new chip fabrication plants increases exponentially as new features get smaller” • Wires carved on silicon by standard lithography methods generate too much heat

Limitations of current chip fabrication methods (cont). • Physical limitations for example transistors at about 50 nanometers dimensions electrons start obeying quantum laws

Advantages of molecular chip making • Could be relatively easier to make • Potentially cost less than current methods • Molecules can be used to build items that are few nanometers in size • Lack imperfections that arise from etching lines as done in lithography

IBM molecular IC • Uses carbon nanotubes which can be grown into smaller dimensions • Instead of constructing good nanotubes one by one, many are built then defective ones are destroyed on the wafer • Patented method referred to “constructive destruction” • IBM to conduct more research to see if carbon nanotubes outperform silicon transistors

Using germs to build circuits • Research carried out at University of Texas lead by A. Belcher • Hired virus to be a nano-construction worker • Genetically engineered viruses grab dots of zinc sulfide to form viral semiconductors • They are then arranged into highly ordered structures which could be made into nanoscale devices.

Research Progress • The researchers have been able to form nanometer scale semiconductor crystals using these viruses (2-3 nm crystals) • Application of this kind of technology would be sensors, quantum-dot flash memories • Goal is to tinker with viral DNA so as to create desired semiconductor components with the immediate target being a transistor.

Recap • Use of current technology can extend Moore’s Law for few years. • New methods such as discussed in the presentation may offer a cheaper and effective way of extending the law in the long term • Challenge for computer scientists to design systems that can fully utilize the changing integrated circuits

References • Fairley, P. Germs that build Circuits. IEEE Spectrum Nov. 2003 pg 37 • Savage, N. A revolutionary Chipmaking Technique. IEEE Spectrum Nov. 2003 pg 18 • International Technology Roadmap for Semiconductors. Executive Summary 2003 • Rotman, D. Molecular computing. Technology Review. May 2000 v103 • Service, R. Assembling nanocircuits from Bottom up. Science August 2001 v293