RTL Projektovanje

RTL Projektovanje. RTL Projektovanje. Projektovanje na registarskom (mikroarhitekturalnom) nivou apstrakcije Sistem se opisuje do nivoa registara i kombinacionih blokova S vi registri imaju zajednički takt (s inhroni sistemi ) RTL metodologija : Konverzija algoritma u RTL hardver

RTL Projektovanje

E N D

Presentation Transcript

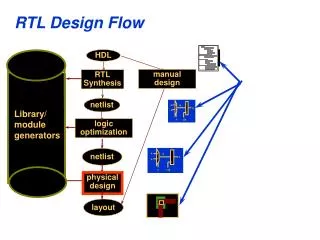

RTL Projektovanje • Projektovanje na registarskom (mikroarhitekturalnom) nivou apstrakcije • Sistem se opisuje do nivoa registara i kombinacionih blokova • Svi registri imaju zajednički takt (sinhroni sistemi) • RTL metodologija: • Konverzija algoritma u RTL hardver • Do nivoa taktnih ciklusa opisuje ponašanje digitalnog sistema • Opis se kreira u VHDL-u, simulira u VHDL simulatoru i sintetiše alatom za sintezu Arhitektura mikrosistema

Algoritam size = 4; sum = 0; for i in (0 to size-1) do { sum = sum + a(i);} q = sum / 8; r = sum rem 8; if(r > 3) { q = q + 1;} outp = q; Detaljan opis toka izvršenja nekog zadatka ili postupka rešavanja nekog problema u vidu sekvence akcija ili koraka Osnovne karakteristika algoritma: Sekvencijalno izvršenje - ˝naredba po naredba˝ u strogo definisanom redosledu Korišćenje promenljivih - ime promenljive ukazuje na simboličku adresu memorijske lokacije gde se smešta vrednost promenljive. Pseudo-kod Prilagođen načinu rada računara Arhitektura mikrosistema

Pseudo-kod u VHDL . . . CONSTANT size : INTEGER := 4; SIGNAL outp : STD_LOGIC_VECTOR(7 DOWNTO 0); . . . PROCESS(a) VARIABLE sum,q,r : STD_LOGIC_VECTOR(7 DOWNTO 0); BEGIN sum := a(0); FOR i IN 1 TO size-1 LOOP sum := sum + a(i); END LOOP; q <= „000“ & sum(7 DOWNTO 3); r <= „00000“ & sum(2 DOWNTO 0); outp <= q + 1 WHEN (r > 3) ELSE q; END PROCESS; size = 4; sum = 0; for i in (0 to size-1) do { sum = sum + a(i);} q = sum / 8; r = sum rem 8; if(r > 3) { q = q + 1;} outp = q; Direktno prevođenje Arhitektura mikrosistema

Pseudo-kod u VHDL Promenljive postaju signali, a operacije hardverski kombinacioni blokovi Nakon razmotavanja FOR LOOP petlje sum0 := a(0); sum1 := sum0 + a(1); sum2 := sum1 + a(2); sum3 := sum2 + a(3); q <= „000“ & sum(7 DOWNTO 3); r <= „00000“ & sum(2 DOWNTO 0); outp <= q + 1 WHEN (r > 3) ELSE q; OK: Pojedine operacije se obavljaju u paraleli, što dovodi do ubrzanja rada NOT OK: Rešenje nije univerzalno Šta ako se size promeni s 4 na 20? - umesto 3, biće potrebno 19 sabirača Šta ako size nije konstanta, već promenljiva? - Hardver ne može dinamički da se ˝širi˝ i ˝skuplja˝ Arhitektura mikrosistema

Realizacija algoritma u hadveru • Registri se koriste kao zamena za promenljive • Hardver koji obavlja operacije sadržane u algoritmu (kao npr. +, -, *, ...) realizuju se u vidu funkcionalnih jedinica (sabirač, oduzimač, množač ...). • Staza podataka (data path) = Registri + funkcionalne jedinice + mux i veze za povezivanje reg. i funkc. jed. • Hardver koji reguliše redosled izvršenja operacija u stazi podataka realizuje se u vidu upravljačke jedinice- konačni automat Arhitektura mikrosistema

Algoritam ->RTL hardver Naredba registarskog prenosa Obavlja se u JEDNOM taktnom ciklusu Algoritamski korak Promenljive Registri Arhitektura mikrosistema

Naredba registarskog prenosa rdest ← f(rsrc1, rsrc2, ..., rsrcn) Izvršava se u jednom taktnom ciklusu: Odredišni registar Izvorni registri Funkcija - bilo koja funkcija koja se može realizovati u hadveru u vidu kombinacione mreže Izračunavanje funkcije Upis u rdest Na izlazima izvornih reg. dostupne su nove vrednosti Arhitektura mikrosistema

Naredbe registarskog prenosa - primeri Arhitektura mikrosistema

Realizacija naredbe registarskog prenosa r1 ← r1 + r2 Arhitektura mikrosistema

Šta ako više naredbi registarskog prenosa imaju isti odredišni registar ? r1 ← 1 r1 ← r1 + r2 r1 ← r1 + 1 r1 ← r1 MUX Bira narebu koja će se izvršiti Staza podataka Arhitektura mikrosistema

Paralelno izvršenje operacija Izračunavanje koje treba realizovati u hardveru Promenljive postaju registri, a programske naredbe postaju naredbe registarskog prenosa x = A; y = B; y = x + y; y = y + 1; x = x + 1; ciklus 1: rx ← A; ciklus 2: ry ← B; ciklus 3: ry ← rx + ry; ciklus 4: ry ← ry + 1; ciklus 5: rx ← rx + 1; U hardveru je dopušteno paralelno izvršenje međusobno nezavisnih operacija Pralelizacija dovodi do ubrzanja rada ciklus 1: rx ← A; ry ← B; ciklus 2: ry ← rx + ry; ciklus 3: ry ← ry + 1; rx ← rx + 1; Arhitektura mikrosistema

Staza podataka ciklus 1: rx ← A; ry ← B; ciklus 2: ry ← rx + ry; ciklus 3: ry ← ry + 1; rx ← rx + 1; Staza podataka nije dovoljna ! Arhitektura mikrosistema

Upravljačka jednica ciklus 1: rx ← A; ry ← B; ciklus 2: ry ← rx + ry; ciklus 3: ry ← ry + 1; rx ← rx + 1; Opisuje se u vidu konačnog automata U svakom taktnom ciklusu bira operacije koje će se izvršiti u stazi podataka Arhitektura mikrosistema

Blok dijagram RTL sistema Sadrži hardverske resurse: Registre Funkcionalne jedinice Multipleksere i Veze Sprovodi algoritam: U svakom taktnom ciklusu bira operacije koje će se izvršiti u stazi podataka. Realizuje se u vidu konačnog automata Arhitektura mikrosistema

Primer složene staze podataka U svakom taktnom ciklusu može da obavi nekoliko od više različitih naredbi registarskog prenosa Selekcioni signali i tatkni signal nisu prikazani Višefunkcionalne jedinice Arhitektura mikrosistema

ASMD dijagram (ASM + Data patah) ASMD dijagram: Sadrži naredbe registarskog prenosa - definiše rad celog sistema (upravljačka jedinica + staza podataka) ASM dijagram: definiše rad upravljačke jedinice start, z, a0 - ulazni signali ia, ea, eb, rdy - izlazni signali Arhitektura mikrosistema

Odložena dodela y je signal koji je aktivan za sve vreme dok je sistem u stanju S1 y je neaktivan. Kao da piše: y=´0´ r1 zadržava (memoriše) tekuću vrednost.Kao da piše: r1←r1 U toku stanja S1 izračunava se r1+r2, ali se upis u r1 vrši tek sledećom ivicom takta, onda kada sistem prelazi u S2 ! Arhitektura mikrosistema

Pristupi projektovanju • Dva pristupa rešavanju problema: • ¨odozdo-naviše¨ (bottom-up) • ¨odozgo-naniže¨ (top-down) Arhitektura mikrosistema

Projektovanje ¨odozdo-naviše¨ • ¨Odozdo-naviše¨ (bottom-up) • Projektant rešava izdvojene detalje celokunog problema koje potom ugrađuje u konačno rešenje • Rešeni detalji se obično međusobo ne uklapaju idealno • Najveći deo ukupnog projektantskog vremena troši na uklapanje nezavisnih detalja, što često uključuje i prepravku već rešenih delova opšteg problema • Nije pogodno za projektovanje složenih digitalnih sistem Interfejs Komponenta Arhitektura mikrosistema

Projektovanje ¨odozgo-naniže¨ • Projektant započinje rad na problemu razradom globalnog plana • sveobuhvatno sagledavanje problema, • razrada strategije rešavanja problema, • dekompozicija problema na potprobleme manjeg obima • definisanje odnosa (interfejsa) između potproblema • projektant ne rešava odmah uočene potprobleme, već ih tretira kao apstraktne sklopove (crne kutije) koje međusobno uklapa i povezuje • U nastavku • Projektant razrađuje i rešava potprobleme • Problem uklapanja ne postoji (interfejsi su definisani u prvoj fazi) Arhitektura mikrosistema

Projektovanje ¨odozgo-naniže¨ - faze projektovanja • Faze • Opis ponašanja (sistem koja se projektuje opisuje se na algoritamskom nivou, npr. u vidu ASMD dijagrama) • Razrada (podela sistema na dva upravljačku jedinicu i staza podataka) • Realizacija(realizacija hardvera sistema) Arhitektura mikrosistema

Opis ponašanja • Najvažnija faza celokupnog procesa projektovanja • Sistem koja se projektuje opisuje se na algoritamskom nivou, npr. u vidu ASMD dijagrama • Sistem se tretira kao crna kutija sa naznačenim ulazima i izlazima koja se ponaša na način koji je opisan algoritmom Arhitektura mikrosistema

Opis ponašanja - Interfes • Interfejs (značenje reči) - mesto na kome se dva nezavisna sistema susreću ili spajaju (ili sredstvo koje koriste) radi zajedničkog dejstva ili međusobne komunikacije. • Digitalni sistem u toku rad ineraguje sa svojim okruženjem (drugi digitalni sistemi, ne-digitalni uređaji, pa čak i čovek koji posredstvom odgovarajućih ulazno-izlaznih uređaja komunicira sa sistemom) • Za definisanje interfesa potrebno je znati koje informacije se razmenjuju između sistema i okruženja i na koji način sistem komunicira sa okruženjem • Specifikacija interfejsa digitalnog sistema uključuje specifikaciju ulaza i izlaza (tj. portova) proširenu pravilima za korišćenje sistema od strane korisnika Arhitektura mikrosistema

Opis ponašanja - Interfejs • Dva tipa ulaznih i izlaznih informacija: • Upravljački i statusni signali (najčešće jednobitni signali) • Upravljački ulazi - iniciraju naku aktivnost sistema • Statusni ulazi - sistem dobija informaciju o trenutnom stanju okruženja • Upravljački izlazi - sistem inicira neku aktivnost u okruženju • Statusni izlazi - obaveštava okruženje o svom trenutnom stanju • Signali takta i resetovanja - prisutni kod svih sistema • Podaci • Ulazni podaci - informacija koju sistem treba da obradi • Izlazni podaci - rezultat obrade Arhitektura mikrosistema

Interfes - Primer (Sekvencijalni delitelj) • Pre aktiviranja upravljačkog ulaza start (start=1) korisnik, treba da postavlja deljenik i delilac na ulazima podatak x i y. Korisnik ne sme da menja x i y za vreme dok traje izračunavanje (dok je rdy=0). • Trajanje signala start mora biti tačno jedan taktni period. • Korisnik je u obavezi da pre sledećeg aktiviranja signala start čeka barem dva taktna ciklusa nakon što je sistem završio prethodno izračunavanje Spada u specifiakciju interfejsa Statusni izlaz Upravljački ulaz Ulazi podataka Izlaz podataka Arhitektura mikrosistema

Interfes - Primer (Handshake interfejs) • Handshake - način koordinacije dva podsistema putem dva signala: • req (request - zahtev) i • ack (acknowladge - potvrda) Arhitektura mikrosistema

Interfes - Primer (Handshake interfejs) Prijemnik Predajnik Arhitektura mikrosistema

Konverzija algoritma u ASMD dijagram Osnova za hardversko rešenje Osnova za softversko rešenje datog problema B = 0; while(A≠0) do if(A0 = 1) then B = B + 1; end if; A = A >> 1; end while; ? Dozvoljava paralelizam (sve operacije obuhvaćene jednim stanjem izvršavaju se istovremeno) Nameće diskretizaciju vremena(jedno stanje, jedan taktni ciklus) Sekvencijalno izvršenje algoritamskih koraka Ne sadrži informaciju o trajanju operacija Arhitektura mikrosistema

Paralelizacija sekvencijalnog kôda Softverski blok naredbi - sekvencijalno izvršenje ASMD - sve naredbe u bloku se izvršavaju paralelno. maksimalan paralelizam - neispravno rešenje jer nisu uvažene zavisnosti između naredbi ASMD - sekvencijalno izvršenje naredbi Ispravno (očuvane su sve zavisnosti), ali sporo ASMD - Optimalno rešenje Nezavisne naredbe u paraleli Arhitektura mikrosistema

Konverzija algoritma u (sekvencijalni) ASMD dijagram • Algoritam je teže predstaviti u obliku ASMD dijagrama nego u obliku softverskog pseudo koda. • => Opis ponašanja digitalnog sistema tipično počinje kreiranjem softverskog algoritma, koji se potom konvertuje u ekvivalentni ASMD dijagram • Pravila za konverziju: • Svaka naredba dodele iz softverskog algoritma prevodi se u naredbu registarskog prenosa koja se smešta u zaseban blok stanja ASMD dijagrama . • Svaka naredba grananja (npr. if, while) iz softverskog algoritma se prevodi u prazan blok stanja posle kojeg sledi blok grananja s upisanom relacijom iz softverske naredbe. Arhitektura mikrosistema

Primer direktne konverzija algoritma u ASMD dijagram - sekvencijalni delitelj Bez TEST, ispitivanje r1>=y koristilo bi staru vrednost r1 !!! r1 = x; r2 = 0; while (r1 >= y) { r2 = r2 + 1; r1 = r1 – y;} Izlaz iz r2 Arhitektura mikrosistema

ASM dijagram sekvencijalnog deliteljaOptimizacija (eliminacija stanja TEST) 4+3q 3+2q Arhitektura mikrosistema

ASM dijagram sekvencijalnog deliteljaOptimizacija (eliminacija stanja INIT) Algoritmaski ispravno. Problem u korisničkom interfejsu: rezultat (u r2) je dostupan za očitavanje samo 1 taktni ciklus Arhitektura mikrosistema

ASM dijagram sekvencijalnog deliteljaOptimizacija (eliminacija stanja INIT) Uvodi se još jedan registar (r3) koji čuva rezultat 2+3q Šta ako je količnik 0 ? Arhitektura mikrosistema

ASM dijagram sekvencijalnog deliteljaOptimizacija (Paralelizacija petlje) Neuspešni pokušaji Preuranjen upis u r3 Arhitektura mikrosistema

ASM dijagram sekvencijalnog deliteljaOptimizacija (Paralelizacija petlje) 2+q Stanje C123 se izvršava jedanput više, ali se zato u r3 upisuje jadnput manje Arhitektura mikrosistema

ASM dijagram sekvencijalnog deliteljaOptimizacija (Eliminacija stanja N3) 2+q Arhitektura mikrosistema

ASM dijagrami Milijevog tipa Uslovne operacije Arhitektura mikrosistema

ASM dijagram sekvencijalnog deliteljaMilijeva verzija (Eliminacija stanja INIT) r2 se resetuje u stanju PASIVO, pod uslovom ako je start=1 Umesto da uvedemo r3 Problem s preranim brisanjem r2 u stanju PASIVNO Arhitektura mikrosistema

ASM dijagram sekvencijalnog deliteljaMilijeva verzija (Spajanje stanja C1 i C2) r2 se inkrementira jedanput više Arhitektura mikrosistema

ASM dijagram sekvencijalnog deliteljaMilijeva verzija (Spajanje stanja C1 i C2) 2+q Arhitektura mikrosistema

ASM dijagram sekvencijalnog deliteljaMilijeva verzija(Ranije postavljanje signala rdy) 2+qtakta i 2 registra Arhitektura mikrosistema

Razrada • Cilj da polazni problem, prethodno precizno opisan ASM dijagramom, podeliti na dva dela: • staza podataka • registri za čuvanje vrednosti promenljivih; • kombinaciona logika za obavljanje izračunavanja iz naredbi registarskog prenosa i relacija. • upravljačku jedinicu - sprovodi algoritam Arhitektura mikrosistema

Projektovanje staze podataka r1 ← x r1 ← r1-y r2 ← 0 r2 ← r2 + 1 r3 ← r2 r1 >= y registar + oduzimač brojač registar komparator Arhitektura mikrosistema

Projektovanje staze podataka(metodička staza podataka) r1 ← x r1 ← r1-y r2 ← 0 r2 ← r2 + 1 r3 ← r2 r1 >= y registar + oduzimač brojač registar komparator r1 ← x(muxctrl=0, ldr1=1) r1 ← r1-y (muxctrl=1, ldr1=1) r2 ← 0 (clrr2=0) r2 ← r2 + 1 (incr2=1) r3 ← r2 (ldrr3=1) r1 >= y (r1gey) Arhitektura mikrosistema

Projektovanje upravljačke jedinice r1 ← x(muxctrl=0, ldr1=1) r1 ← r1-y (muxctrl=1, ldr1=1) r2 ← 0 (clrr2=1) r2 ← r2 + 1 (incr2=1) r3 ← r2 (ldrr3=1) r1 >= y (r1gey) Arhitektura mikrosistema

Upravljačka jedinica (strukturna varijanta ASM dijagrama) Arhitektura mikrosistema

Staza podataka zasnovana na ALUsekvencijalna staza podataka Na osnovu sekvencijanog ASMD Manja hardverska složenost, ali po cenu dužeg vremena izvršenja Arhitektura mikrosistema

Staza podataka zasnovana na ALUsekvencijalna staza podataka Neoptimizovana ALU Optimizovana ALU Arhitektura mikrosistema