Xilinx XC9500 CPLDs: High-Performance, Lowest Price, Maximum Flexibility

150 likes | 269 Vues

Discover the powerful Xilinx XC9500 CPLDs offering high performance at affordable prices. Featuring versatile macrocell densities, advanced pin-locking technology, and support for various voltages, these CPLDs are the perfect solution for your design needs. With a range of macrocell capacities and ultra-low power consumption, the XC9500 series ensures top-notch reliability and efficiency. Take advantage of the most complete IEEE 1149.1 JTAG system and space-efficient packaging options for streamlined integration into your projects.

Xilinx XC9500 CPLDs: High-Performance, Lowest Price, Maximum Flexibility

E N D

Presentation Transcript

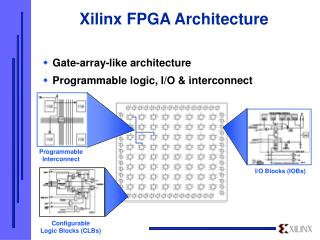

125MHz XC9500 XC9500XL Key Features 200MHz • High performance • tPD = 5ns, fSYS = 178MHz • 36 to 288 macrocell densities • Lowest price, best value CPLD • Highest programming reliability • Most complete IEEE 1149.1 JTAG • Space-efficient packaging, including chip scale pkg XC9500XL Lowest Price Per Macrocell

Advanced, 2ndGeneration Pin-Locking Superior routability with speed Maximum Flexibility 54-input function block fan-in 90 p-terms per output 3 global, locally invertible clocks Global set/reset pin P-term OE per macrocell Clock enable XC9500XL/XV Architecture Embraces In-System Changes

XC9500XL/XV System Features • I/O Flexibility • XL:5v tolerant; direct interface to 3.3v & 2.5v • XV:5v tolerant; direct interface to 3.3v, 2.5v & 1.8V • Input hysteresis on all pins • User programmable grounds • Bus hold circuitry for simple bus interface • Easy ATE integration for ISP & JTAG • Fast, concurrent programming times

3.3v ISP XC9536XL XC9572XL XC95144XL XC95288XL 2.5v ISP XC9536XV XC9572XV XC95144XV XC95288XV Macrocells 36 72 144 288 Usable Gates 800 1600 3200 6400 t ( ns) XC9500XL 5 5 5 7.5 pd t ( ns) XC9500XV 4 5 5 6 pd Registers 36 72 144 288 f XC9500XL 178 178 178 125 SYSTEM XC9500XV 200 178 178 151 Packages PC44 PC44 CS48 CS48 VQ44* VQ44* VQ64 VQ64 TQ100 TQ100 TQ144 TQ144 CS144 PQ208 BG256 FG256* CS280* XC9500XL/XV Family * available in 2Q00

XC9500 5V Family XC9536 XC9572 XC95108 XC95144 XC95216 XC95288 36 72 108 144 Macrocells 216 288 Usable Gates 800 1600 2400 3200 6400 4800 5 7.5 7.5 7.5 15 tPD (ns) 10 36 72 108 144 288 Registers 216 Max. User I/Os 34 72 108 133 192 166 44VQ 44PC 48CSP 44PC 84PC 100TQ 100PQ 84PC 100TQ 100PQ 160PQ 100TQ 100PQ 160PQ Packages 208HQ 352BG 160PQ 208HQ 352BG 3/97

Most Complete JTAG Testability • IEEE Std 1149.1 boundary-scan • Testability & advanced system debug/diagnosis • 8 instructions supported (incl. CLAMP) • Full support on all family members • Industry-standard ISP interface • Complete 3rd party support

FLASH Technology EnablesRapid Die Size Reduction 0.6u/2LM 0.5u/3LM 0.35u/4LM 0.25u/4LM 0.18u/5LM 1.0x DELIVERED 1996 5V 0.5x 1998 DELIVERED 5V 0.3x DELIVERED 3.3V 0.3x 1999 2.5V DELIVERED 0.2x 2000 2.5V On schedule 0.12x 2001 1.8V On schedule • 0.5 µ = 0.5µ transistor with 0.35µ interconnect

Non-Volatile Xilinx CPLD Process Leadership Year used in Year used in SPLD/CPLD Technology Memories SPLD/CPLD Pioneer Bipolar Fuse 1973 1978 MMI (AMD) EPROM 1979 1984 Altera EP-series 5V EEPROM 1986 1991 Lattice ispLSI 5V FLASH 1990 1995 Xilinx XC9500 3.3V FLASH 1993 1998 Xilinx XC9500XL 2.5V FLASH 1996 2000 Xilinx XC9500XV

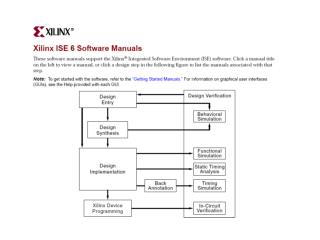

Web-Powered CPLD Software Integrated CPLD Design Environment • FREE, downloadable solution • VHDL, Verilog & ABEL synthesis • Modular, efficient CPLD design On-line CPLD Design Analysis • Accepts any input • Complete XC9500 Series evaluation • On-line pricing, saves money

Density • 12% More M/Cs • 22V10s to 960 M/Cs • Pin-Locking • Industry’s Best • Speed • Fast tPD, fSYS • JTAG • 1149.1 Family Support • Ultra Low Power • CoolRunner • Packaging • TQ/PQ & 0.8mm CSP • Silicon Xpresso • WebFITTER • WebPACK • Technology • True, 0.35u Flash • Reliability • 10,000 program/erase cycles • 20 year data retention Xilinx CPLDsPerformance ISP • Price • Lowest, best value

XC9500 CPLDs - XC9500XL (3.3v) - XC9500 (5v) - XC9500XV (2.5v) Key Features - 36 to 288 macrocells - High performance - Low cost - In-system programmable - Chip scale packages Spartan FPGAs - SpartanXL (3.3v) - Spartan (5v) Key Features - Low cost ASIC replacement - 5K to 40K system gates - High performance - SelectRAM memory - Chip Scale packages Features 1K 5K 40K Xilinx Programmable Logic Solutions System Gates

Chip Scale Packaging Leadership Supports high-growth market segments: Communications, Computers, Consumer New 48-pin CSP: 1/3 size of the VQ44 Uses standard IR techniques for mounting to PC board