EE40 Lec 20 MOS Circuits

430 likes | 933 Vues

EE40 Lec 20 MOS Circuits. Reading: Chap. 12 of Hambley Supplement reading on MOS Circuits http://www.inst.eecs.berkeley.edu/~ee40/fa09/handouts/EE40_MOS_Circuit.pdf. OUTLINE. Bias circuits Small-signal equivalent circuits Examples: Common source amplifier Source follower

EE40 Lec 20 MOS Circuits

E N D

Presentation Transcript

EE40 Lec 20MOS Circuits Reading: Chap. 12 of Hambley Supplement reading on MOS Circuits http://www.inst.eecs.berkeley.edu/~ee40/fa09/handouts/EE40_MOS_Circuit.pdf

OUTLINE • Bias circuits • Small-signal equivalent circuits • Examples: Common source amplifier Source follower Common gate amplifier • Digital Gates • CMOS

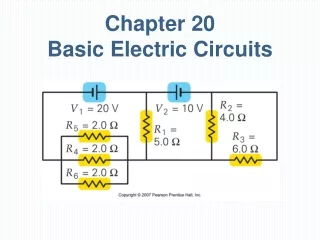

VDD VDD RD RD R1 VG+vin R2 RS Bias Circuits • Use load line to find Quiescent operating point. • Remember no current flow through the gate. Fixed-plus Self-Bias CKT

Steps for MOSFET Circuit Analysis • 1) Look at DC case to find Q point • Use load line technique • All capacitors are open circuit, Inductors are short circuit • Determine Q-point, get gm and rd for small signal AC model • 2) AC Small signal analysis • DC source is ac ground (because there is no AC signal variation). • All capacitors are approximated as short circuit (unless otherwise specified).

+ vo - + + vin v(t) - - Example: Common Source Amplifier VDD RD C R1 C RL VG R2 C RS

+ vo - + + v(t) vin - - Step 1: find Q point VDD Not connected for DC component RD C R1 C VG RL VDS R2 C RS Not connected for DC component

Load line to determine Q Point by graphical method Loadline to determine VGSQ Loadline to determine VDSQ VGSQ From load lines, we get ID and hence gm and rd

Load line to determine Q Point by analytical method Solve VGSQ assume saturation region first IDQ is known, then solve VDSQ Check VDSQ value is consistent with saturation region ( i.e. VDS> VGSQ-Vt) From load lines, we get ID and hence gm and rd

Determination of gm and rd graphically Example: Q point is known to be VGS=2.5V, VDS=6V

Determination of gm and rd by Analytical Models In Saturation Region In Triode Region

Small Signal Model Inverting • For output impedance Rout: • Turn off all independent sources. • Take away load impedance RL

+ vo RL - + + vin v(t) - - Example: Source Follower VDD R1 C VG C R2 RS

+ vo RL - + + vin v(t) - - Step 1: find Q point VDD R1 C VG C R2 RS

Small Signal Model Non-inverting, Voltage Gain <1 Rin high Current gain can be high • For output impedance Rout: • Turn off all independent sources. • Take away RL • Add Vx and find ix Rout is small

+ vo - + + v(t) vin - - Example: Common Gate Amplifier VDD RD C RL VG C RS -VSS

+ vo - + + v(t) vin - - Step 1: find Q point VDD RD C RL VG C RS -VSS

Load line The only difference in all three circuits are the intercepts at the axes. Again from load lines, we get ID and hence gm and rd

Small Signal Model Non-inverting • For output impedance Rout: • Turn off all independent sources. • Take away RL • Add Vx and find ix

Logic Gates : Pull-Up and Pull-Down PMOS or Resistor NMOS or Resistor

Inverter = NOT Gate Vin Vout Ideal Transfer Characteristics Vout Vin V/2 V

vIN = VDD VDD/RD increasing vGS = vIN > VT VDD vGS = vin VT NMOS Inverter: Resistor Pull-Up Voltage-Transfer Characteristic Circuit: vOUT VDD F A iD vIN 0 VT VDD vDS 0

NMOS NAND Gate Output is low only if both inputs are high VDD RD F A Truth Table B

NMOS NOR Gate Output is low if either input is high VDD RD F A B Truth Table

Disadvantages of NMOS Logic Gates • Large values of RD are required in order to • achieve a low value of VLOW • keep power consumption low • Large resistors are needed, but these take up a lot of space.

CMOS Inverter: Intuitive Perspective VDD S G D VOUT VIN D G S SWITCH MODELS CIRCUIT VDD VDD Rp VOUT VOUT VOL = 0 V VOH = VDD Rn Low static power consumption, since one MOSFET is always off in steady state VIN = VDD VIN = 0 V

The CMOS Inverter: Current Flow i I N: sat P: sat VOUT N: off P: lin C V DD VDD S G N: sat P: lin D VIN VOUT B D E A D G N: lin P: sat S N: lin P: off 0 VIN VDD 0

Power Dissipation: Direct-Path Current VDD-VT VT Ipeak 0 tsc Energy consumed per switching period: VDD V DD vIN: S G 0 D i vIN vOUT D G i: S time

CMOS NAND Gate VDD A B Notice that the pull-up network is related to the pull-down network by DeMorgan’s Theorem! F A NMOS, Pull-down PMOS, Pull-up B

CMOS NOR Gate VDD A Notice that the pull-up network is related to the pull-down network by DeMorgan’s Theorem! B F NMOS, Pull-down PMOS, Pull-up A B

Features of CMOS Digital Circuits The output is always connected to VDD or GND in steady state Full logic swing;large noise margins Logic levels are not dependent upon the relative sizes of the devices (“ratioless”) There is no direct path between VDD and GND in steady state no static power dissipation