ARM920T Processor

ARM920T Processor. ARM920T Processor. The ARM920T processor is a member of the ARM9TDMI family of general purpose microprocessors Includes the ARM9TDMI core plus cache and MMU. ARM9TDMI processor: Harvard architecture Increases available memory bandwith

ARM920T Processor

E N D

Presentation Transcript

ARM920T Processor • The ARM920T processor is a member of the ARM9TDMI family of general purpose microprocessors • Includes the ARM9TDMI core plus cache and MMU. • ARM9TDMI processor: • Harvard architecture • Increases available memory bandwith • Simultaneous access to instruction and data memory can be achieved • 5-stage pipeline • 32-bit ARM instruction set and 16-bit THUMB instruction set.

ARM920T Processor • ARM7TDMI • ARM9TDMI Instruction Fetch ThumbARM decompress ARM decode Reg Read Shift ALU Reg Write Reg Select FETCH DECODE EXECUTE Instruction Fetch ARM or Thumb Inst Decode Shift + ALU Memory Access Reg Write Reg Decode Reg Read FETCH DECODE EXECUTE MEMORY WRITE

ARM9TDMI CORE 16K D Cache 16K I Cache Write Buffer MMU MMU Control Logic & BIU Coprocessor, ETM9 & AMBA ASB Interfaces ARM920T Processor • Cached Processor for Platform OS Applications • 16K Instruction & Data Caches • ARMv4 MMU for: PalmOS, EPOC, Linux & WindowsCE • Includes support for Coprocessor and ETM

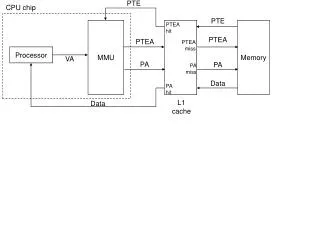

ARM920T MMU • What is an MMU ? • Memory Management Unit • Controls memory access permissions • Translates virtual addresses into physical addresses • MMU consists of • Translation Look-aside Buffer (TLB) • Cache of recently used page translations • Hardware for page table walks • Updates TLB • Access control logic • If MMU is disabled • External address bus will output virtual addresses directly

ARM920T MMU • Virtual to Physical Address Mapping Virtual Memory Translation and checking mechanism. Physical Memory Process D Translation Tables MMU Process C VRAM Process B RAM I TLB ROM D TLB Process A RAM RAM Manager RAM Protection & Aborts

ARM920T MMU • Translation Look-aside Buffer acts as a cache of recent VA to PA translations • Provides translation and access permission information for most memory accesses • For TLB misses, the translation table walking hardware retrieves the information from the translation table in physical memory and the TLB is updated • If the TLB is full, a value will be overwritten using a cyclic scheme • Translation Tables resides in physical memory • Level 1 table is a list of 4096 translations, indexed by bits 31:20 of the virtual address • Entries contain a pointer to a 1MB section of physical memory along with attribute information, or … • A pointer to the base address of a another table, containing pointers to smaller pages of physical memory

ARM920T MMU • Translation Process • Performed by hardware and is transparent to the user • Translation tables created by software Virtual address Check if TLB contains virtual address yes no Get physical address Do translation table walk Get physical address Update TLB

ARM920T MMU • Two Translation Lookaside Buffers (TLBs) • 64-entry Instruction TLB • 64-entry Data TLB • Two-level Hardware table walking : • Address translation • Access control logic with permissions • Highly flexible mapping scheme - supports: • 1MB sections (with permissions) • 64kB large pages (permissions for each subpage of a page) • 4kB small pages (permissions for each subpage of a page) • 1kB tiny pages (with permissions)

ARM920T MMU • MMU usage in Linux • Allows Memory mapping (physical to virtual address) • Allows memory allocation • Allows to safely run several processes, each one has a protected memory area. • Provides protection against direct access to a peripheral’s physical address

ARM920T Caches • What is a cache ? • Small fast memory, local to the processor • Holds copies of recently accessed memory locations • Relies on memory re-use • Only improves performance for slow memory or narrow memory • Reduces bus bandwidth requirements • Reduces power consumption External Memory CPU Cache Bus Interface Address Data

ARM920T Caches • 16KB instruction and data caches • 512 lines of 8 words arranged as a 64-way set-associative cache • MMU must be enabled to enable Dcache 8 words 8 TAG = MVA [ 31 : 8 ] 8 words 7 8 words 6 8 words 5 8 words 4 8 words 3 8 words 2 TAG 8 words 1 64 lines

ARM920T Caches • Cache hit and miss • Cache hit, if region is cachable, data are returned from the cache • Cache miss, an eight-word linefill is performed replacing another entry • Replacement algorithm • Random by default • Round-Robin : entries of each segment are replaced sequentially. More efficient. • Caches operate at processor speed • Max processor speed is 180 Mhz • Max AMBA ASB speed is 60 Mhz

ARM920T Caches • 16-word (64Bytes) write buffer • Lockdown features • Lockdown instruction and data caches independently with a granularity of 1/64 th of cache • Must lockdown the associated TLB entry in the TLB to avoid page table walks during accesses to the locked data or instruction • Provide optimum and predictable execution time