Introduction to Sequential Design

1.24k likes | 1.73k Vues

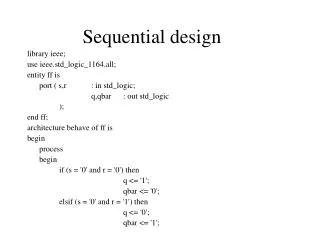

Introduction to Sequential Design. Types of Logic Circuits. Logic circuits can be: Combinational Logic Circuits-outputs depend only on current inputs Sequential Logic Circuits-outputs depends not only on current inputs but also on the past sequence of inputs. Sequential Circuit Models.

Introduction to Sequential Design

E N D

Presentation Transcript

Types of Logic Circuits • Logic circuits can be: • Combinational Logic Circuits-outputs depend only on current inputs • Sequential Logic Circuits-outputs depends not only on current inputs but also on the past sequence of inputs

Combinational Logic Delay Longest delay Shortest delay Longest timing delay = 5ns+5ns+5ns+5ns = 20ns Shortest timing delay = 5ns We will use the longest delay to represent the combinational logic (CL) delay, tcl

Combinational Logic (CL) Cloud Model Tcl=20ns Tcl=20ns

Memory • We will add memory (or registers) to our logic circuits. This will allow us to design sequential circuits.

Registers • We will represent registers with the following block diagram Clock and reset are control signals Ns and ps are data signals

Sequential Systems Block Diagrams

Sequential Systems General Block Diagram Next State Present State Output Vector Input Vector Clock Feedback Path Reset CL= Combinational Logic Cloud Reg= D Registers

Sequential SystemsGeneral Block Diagram Next State Present State Output Vector Input Vector Clock Feedback Path Reset X is the input data vector Y is the output data vector

Sequential SystemsBlock Diagram Next State Present State Output Vector Input Vector Clock Feedback Path Reset Ns is the next state data vector Ps is the present state data vector

Sequential SystemsBlock Diagram Next State Present State Output Vector Input Vector Clock Feedback Path Reset Notice we have a feedback path which combines the ps data vector with the input vector to generate a new ns data vector.

Sequential SystemsBlock Diagram Next State Present State Output Vector Input Vector Clock Feedback Path Reset Mathematically, we say Or, ns is a function F of X and ps and Y is a function H of ps.

F Logic Register Example Circuit Schematic ns ps X input H Logic (buffer) Block Diagram

F Logic Register Example Circuit Schematic ns ps X input H Logic (buffer) State Equations

Finite State Machine (FSM) General Models

Moore FSM General Block Diagram Next State Present State Output Vector Input Vector Clock Feedback Path Reset CL= Combinational Logic Cloud Reg= D Registers

Moore FSM State Equations Next State Present State Output Vector Input Vector Clock Feedback Path Reset State Equations

Mealy FSM Block Diagram and State Equations Next State Present State Input Vector Output Vector Feedback Path Output Y is also a function of input X

Mealy-Moore FSM Block Diagram and State Equations Present State Next State Input Vector Mealy Outputs Moore Outputs

State Bubble Example Conditional Transition Unconditional Transition State name = S0 State value = 00 Y = 0 for this state We leave this state if upn=1, We remain in this state if upn=0

Memory Devices • Data Latch (D-latch) • Flip-flops (edge triggered) • D-FF, D Register • JK-FF • T-FF

D-FF Positive Edge TriggeredBlock Diagram Symbol 4 inputs: D,Clk,Pre,Rst One output: Q D = Data Input Clk = Clock Input Pre = Preset Input Rst = Reset Input

D-FF Truth Table Symbol Truth Table Equation (rising clock)

D-FF Truth Table Symbol Truth Table Equation (rising clock) Pre= Preset Input (active low) Rst = Reset Input (active low) Highest priority

D-FF Truth Table Symbol Truth Table Equation (rising clock) D = Data Input Clk = Clock input Qn = Register Output

Example– 2-bit Up Counter • State Diagram Clock is implied

Example – 2-bit Up Counter • State Table State Value Assignment Let Output Vector Let S0 = reset state

Example – 2-bit Up Counter • Truth Table

Example – 2-bit Up Counter • Excitation Equations

Moore FSM Next State Present State Output Vector Input Vector Clock Feedback Path Reset State Equations

Reg Block F Logic Y Vector H Logic Logic Diagram No X Vector in this Example No H Logic needed

Example 3– 2-bit Down Counter • State Diagram Clock is implied

Example – 2-bit Down Counter • State Table Let Let S0 = reset state

Example – 2-bit Down Counter • Truth Table

Example – 2-bit Down Counter • Excitation Equations

Recall Moore FSM Next State Present State Output Vector Input Vector Clock Feedback Path Reset State Equations

Logic Diagram Reg Block F Logic Y Vector H Logic No X Vector in this Example

Example 4 – 2-bit Up/Down Counter • State Diagram

Example – 2-bit Up/Down Counter • State Diagram Shorthand Notation

Example – 2-bit Up/Down Counter • State Table Let Let S0 = reset state

Example – 2-bit Up/Down Counter • Truth Table