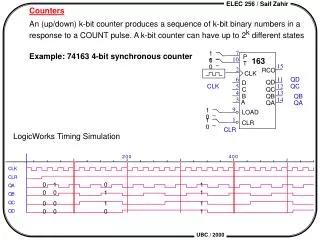

Binary Counters

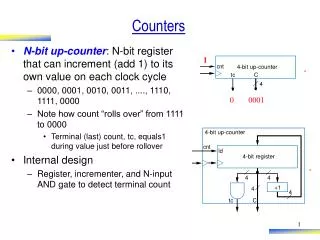

This guide explores various types of 3-bit binary counters, focusing on up, down, and up-down counters. Each counter's functioning is analyzed through its state transition tables, equations, and simulations. Key components like clock pins, output pins, and truth tables for 7-segment displays are examined to provide a comprehensive understanding of binary counting operations. We'll delve into practical implementations with push-button switches, output vectors, and segmentation for real-world applications, enhancing your grasp of digital design.

Binary Counters

E N D

Presentation Transcript

Binary Counters Module M10.3 Section 7.2

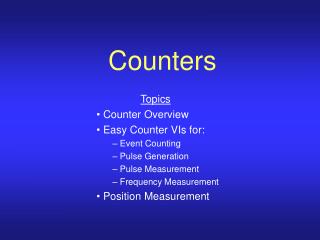

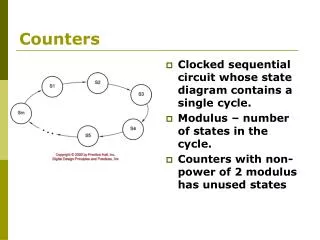

Counters • 3-Bit Up Counter • 3-Bit Down Counter • Up-Down Counter

State Q2 Q1 Q0 Q2.D Q1.D Q0.D D Q Q0.D Q0 CLK !Q s0 0 0 0 0 0 1 s1 0 0 1 0 1 0 s2 0 1 0 0 1 1 s3 0 1 1 1 0 0 s4 1 0 0 1 0 1 s5 1 0 1 1 1 0 s6 1 1 0 1 1 1 s7 1 1 1 0 0 0 D Q Q1.D Q1 CLK !Q D Q Q2.D Q2 CLK !Q Divide-by-8 Counter

State Q2 Q1 Q0 Q2.D Q1.D Q0.D s0 0 0 0 0 0 1 s1 0 0 1 0 1 0 s2 0 1 0 0 1 1 s3 0 1 1 1 0 0 s4 1 0 0 1 0 1 s5 1 0 1 1 1 0 s6 1 1 0 1 1 1 s7 1 1 1 0 0 0 Divide-by-8 Counter Q1 Q0 00 01 11 10 Q2 1 0 1 1 1 1 Q2.D Q2.D = !Q2 & Q1 & Q0 # Q2 & !Q1 # Q2 & !Q0

State Q2 Q1 Q0 Q2.D Q1.D Q0.D s0 0 0 0 0 0 1 s1 0 0 1 0 1 0 s2 0 1 0 0 1 1 s3 0 1 1 1 0 0 s4 1 0 0 1 0 1 s5 1 0 1 1 1 0 s6 1 1 0 1 1 1 s7 1 1 1 0 0 0 Divide-by-8 Counter Q1 Q0 00 01 11 10 Q2 1 1 0 1 1 1 Q1.D Q1.D = !Q1 & Q0 # Q1 & !Q0

State Q2 Q1 Q0 Q2.D Q1.D Q0.D s0 0 0 0 0 0 1 s1 0 0 1 0 1 0 s2 0 1 0 0 1 1 s3 0 1 1 1 0 0 s4 1 0 0 1 0 1 s5 1 0 1 1 1 0 s6 1 1 0 1 1 1 s7 1 1 1 0 0 0 Divide-by-8 Counter Q1 Q0 00 01 11 10 Q2 1 1 0 1 1 1 Q0.D Q0.D = ! Q0

div8cnt.abl MODULE Div8Cnt TITLE 'Divide by 8 Counter, D. Hanna, 7/20/02' DECLARATIONS " INPUT PINS " PB PIN 10; " push-button switch (clock) " OUTPUT PINS " Q2..Q0 PIN 37,36,35 ISTYPE 'reg buffer'; " LED 6..8 Q = [Q2..Q0]; " 3-bit output vector [A,B,C,D,E,F,G,DP] PIN 15,18,23,21,19,14,17,24 ISTYPE 'com'; Segments = [A,B,C,D,E,F,G]; " 7-segment LED display

EQUATIONS Q.c = PB; Q2.d = !Q2 & Q1 & Q0 # Q2 & !Q1 # Q2 & !Q0; Q1.d = !Q1 & Q0 # Q1 & !Q0; Q0.d = !Q0; DP = PB; " decimal point @radix 16; truth_table ( Q -> Segments ) " 7-segment display 0 -> 7E; 1 -> 30; 2 -> 6D; 3 -> 79; 4 -> 33; 5 -> 5B; 6 -> 5F; 7 -> 70; END Div8Cnt Clock div8cnt.abl (cont’d)

Simulation File, div8cnt.si CUPL Simulation File

div8cnt.si CUPL Simulation File

CUPL Simulation Output File

Counters • 3-Bit Up Counter • 3-Bit Down Counter • Up-Down Counter

State Q2 Q1 Q0 Q2.D Q1.D Q0.D D Q Q0.D Q0 CLK !Q s0 0 0 0 1 1 1 s1 0 0 1 0 0 0 s2 0 1 0 0 0 1 s3 0 1 1 0 1 0 s4 1 0 0 0 1 1 s5 1 0 1 1 0 0 s6 1 1 0 1 0 1 s7 1 1 1 1 1 0 D Q Q1.D Q1 CLK !Q D Q Q2.D Q2 CLK !Q 3-Bit Down Counter

State Q2 Q1 Q0 Q2.D Q1.D Q0.D s0 0 0 0 1 1 1 s1 0 0 1 0 0 0 s2 0 1 0 0 0 1 s3 0 1 1 0 1 0 s4 1 0 0 0 1 1 s5 1 0 1 1 0 0 s6 1 1 0 1 0 1 s7 1 1 1 1 1 0 3-Bit Down Counter Q1 Q0 00 01 11 10 Q2 1 0 1 1 1 1 Q2.D Q2.D = !Q2 & !Q1 & !Q0 # Q2 & Q1 # Q2 & Q0

State Q2 Q1 Q0 Q2.D Q1.D Q0.D s0 0 0 0 1 1 1 s1 0 0 1 0 0 0 s2 0 1 0 0 0 1 s3 0 1 1 0 1 0 s4 1 0 0 0 1 1 s5 1 0 1 1 0 0 s6 1 1 0 1 0 1 s7 1 1 1 1 1 0 3-Bit Down Counter Q1 Q0 00 01 11 10 Q2 1 1 0 1 1 1 Q1.D Q1.D = !Q1 & !Q0 # Q1 & Q0

State Q2 Q1 Q0 Q2.D Q1.D Q0.D s0 0 0 0 1 1 1 s1 0 0 1 0 0 0 s2 0 1 0 0 0 1 s3 0 1 1 0 1 0 s4 1 0 0 0 1 1 s5 1 0 1 1 0 0 s6 1 1 0 1 0 1 s7 1 1 1 1 1 0 3-Bit Down Counter Q1 Q0 00 01 11 10 Q2 1 1 0 1 1 1 Q0.D Q0.D = ! Q0

Counters • 3-Bit Up Counter • 3-Bit Down Counter • Up-Down Counter

Up-Down Counter Up-Down Counter clock Q0 Q1 Q2 UD UD = 0: count up UD = 1: count down

Up-Down Counter UD Q2 Q1 Q0 Q2.D Q1.D Q0.D UD Q2 Q1 Q0 Q2.D Q1.D Q0.D 0 0 0 0 0 0 1 0 0 0 1 0 1 0 0 0 1 0 0 1 1 0 0 1 1 1 0 0 0 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 0 1 1 1 0 1 1 1 0 0 0 1 0 0 0 1 1 1 1 0 0 1 0 0 0 1 0 1 0 0 0 1 1 0 1 1 0 1 0 1 1 0 0 0 1 1 1 1 0 1 1 0 0 1 1 1 0 1 0 1 1 1 1 1 1 1 0 Up-Counter Down-Counter

Up-Down Counter Q1 Q0 00 01 11 10 UD Q2 00 01 11 10 Make Karnaugh maps for Q2.D, Q1.D, and Q0.D