3-Tap FIR Filter Optimizations

150 likes | 514 Vues

3-Tap FIR Filter Optimizations. By: Jeff Rybczynski CMPE 222. 3-Tap FIR Filter Design. FIR Filter Control. Six States meaning 3 bit State Variable Each Multiply is in a separate state Asynchronous Reset. FIR Filter Data Path. 3 Independent Multiply Operations

3-Tap FIR Filter Optimizations

E N D

Presentation Transcript

3-Tap FIR Filter Optimizations By: Jeff Rybczynski CMPE 222

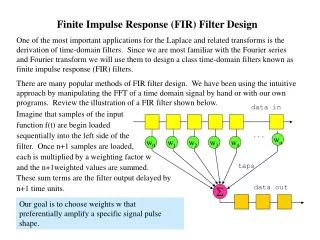

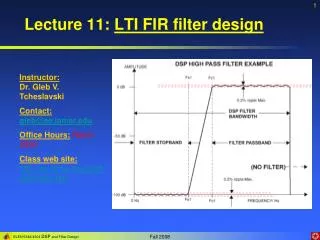

3-Tap FIR Filter Design FIR Optimization – Jeff Rybczynski

FIR Filter Control • Six States meaning 3 bit State Variable • Each Multiply is in a separate state • Asynchronous Reset FIR Optimization – Jeff Rybczynski

FIR Filter Data Path • 3 Independent Multiply Operations • 3 Independent Addition Operations • Not order dependent FIR Optimization – Jeff Rybczynski

Optimized FIR Control • Take out extra calculate steps and place all the multiplies in one CALC state • Add the values from the multiply step together in ADD state • Place value directly into result before you raise output_ready FIR Optimization – Jeff Rybczynski

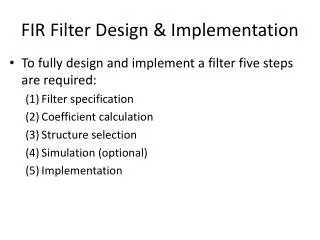

Changes to the Verilog Code • Original Verilog Code 3'b100 : begin output_ready <= 1'b0; rin <= sample; end 3'b110 : acc <= rin * 24'h702a78; 3'b111 : acc <= rs0 * 24'h800000 + acc; 3'b101 : acc <= rs1 * 24'h4fd547 + acc; 3'b001 : begin output_ready <= 1'b1; result <= acc; rs1 <= rs0; rs0 <= rin; end default : begin acc <= 24'h000000; output_ready <= 1'b0; end FIR Optimization – Jeff Rybczynski

Changes to the Verilog Code • Optimized Code 2'b00 : begin output_ready <= 1'b0; rin <= sample; end 2'b10 : begin temp1 <= rin * 24'h702a78; temp2 <= rs0 * 24'h800000; temp3 <= rs1 * 24'h4fd547; end 2'b11 : begin result <= temp1 + temp2 + temp3; rs1 <= rs0; rs0 <=rin; output_ready <=1’b1 end 2'b01 : output_ready <= 1'b0; FIR Optimization – Jeff Rybczynski

6x6 Multiplier Array Multiplier • Similar to how you multiply by hand • Cascading Array multiplier blocks FIR Optimization – Jeff Rybczynski

Array Multiplier Block FIR Optimization – Jeff Rybczynski

A3=1 A2=0 A1=1 A0=1 0 0 0 0 0 0 0 0 B0=1 1 0 1 1 0 1 0 0 0 1 0 1 0 B1=0 0 0 0 0 A B CO CI S A B CO CI S A B CO CI S A B CO CI S A B CO CI S A B CO CI S A B CO CI S A B CO CI S A B CO CI S A B CO CI S A B CO CI S A B CO CI S A B CO CI S A B CO CI S A B CO CI S A B CO CI S 0 0 0 1 0 0 0 1 0 B2=1 1 0 1 1 0 1 0 0 1 0 0 1 0 B3=1 1 0 1 1 0 1 0 1 1 0 0 1 0 A B CO CI S A B CO CI S A B CO CI S A B CO CI S 0 0 1 1 0 1 0 0 0 1 1 1 1 Array Multiplier FIR Optimization – Jeff Rybczynski

Add Array Multiplier to Verilog Code • New Code: • Old Code: temp1 <= rin * 24'h702a78; temp2 <= rs0 * 24'h800000; temp3 <= rs1 * 24'h4fd547; array_multi a(temp1,rin, 24'h702a78); array_multi b(temp2,rs0, 24'h800000); array_multi c(temp3,rs1, 24'h4fd547); FIR Optimization – Jeff Rybczynski

FIR Designs FIR Optimization – Jeff Rybczynski