Xilinx Cadence Alliance Series

610 likes | 862 Vues

Xilinx Cadence Alliance Series. Technology through Teamwork. Agenda. Product Overview Design Flow Methodology XACT 5.2.1 to M1 Migration. Product Overview. Cadence FPGA Products XACT (pre-M1) Cadence Interface Cadence Releases Xilinx M1.3 Development System Xilinx Releases.

Xilinx Cadence Alliance Series

E N D

Presentation Transcript

Xilinx Cadence Alliance Series Technology through Teamwork

Agenda • Product Overview • Design Flow Methodology • XACT 5.2.1 to M1 Migration

Product Overview • Cadence FPGA Products • XACT (pre-M1) Cadence Interface • Cadence Releases • Xilinx M1.3 Development System • Xilinx Releases

Cadence FPGA Products Supported in XACTstep 5.2.x, but no longer supported in the Xilinx M1.3 release

XACT Cadence Interface (pre-M1) Effective 11/1/96, Cadence no longer distributes the Xilinx Core tools. Xilinx has exclusive ownership of both maintenance and support of these tools.

Cadence Releases Compatible with Xilinx M1.3 Release

M1 Software Products Cadence interface libraries and netlisters must be obtained from Cadence

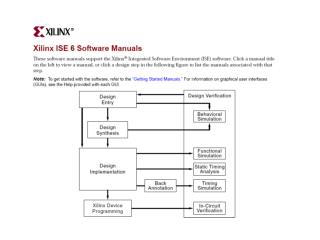

Design Flow Methodology • M1 Flow • Schematic Entry • HDL Synthesis • M1 Implementation • Verilog Timing Simulation • Summary

Design Source Integration K nowledge-Driven Implementation Point Verification Xilinx M1 Design Flow • Schematic entry: CONCEPT • HDL entry: SYNERGY • Interface netlist: EDIF • Device Implementation: Xilinx Design Manager & Flow Engine • Interface Netlist: Verilog or VHDL • Simulator: Verilog-XL or VITAL-compliant simulator (Leapfrog)

Symbol Body Genview module.v Schematic Design LogiBLOX Verilog *.v module.ngo User-Specified Verilog Testbench EDIF *.edf .vf file .v file ConstraintsFile - netlister from Cadence Concept Schematic Flow Schematic Entry Optional Concept Unified Sch. Libraries LogiCores CONCEPT Via HDL_Direct CONCEPT2XIL -sim_only CONCEPT2XIL Knowledge Driven FunctionalSimulation Verilog Unified Simulation Libraries Implementation Tools Verilog-XL

Optional Synergy Synthesis Libraries LogiBLOX VHDL or Verilog HDL Timing constraints module.ngo Structural Verilog *.v .NCF User-Specified Verilog Testbench EDIF *.edf FunctionalSimulation Knowledge Driven Verilog Unified Simulation Libraries ConstraintsFile Verilog-XL Implementation Tools - netlister from Cadence Synergy Synthesis Flow HDL Entry LogiCores SYNERGY RTL Behavioral Simulation VLOG2XIL Post-Synthesis Functional Simulation

Symbol Body Timing Concept Unified Schematic Libraries Genview .NCF .NGO Structural Verilog *.v Structural Verilog *.v User-Specified Verilog Testbench .vf file EDIF *.edf .v file .UCF ConstraintsFile - netlister from Cadence Concept/Synergy Mixed Mode Flow Concept top level schematic Schematic Entry HDL Entry Synergy Synthesis Libraries SYNERGY CONCEPT LogiBLOX CONCEPT2XIL -sim_only CONCEPT2XIL Knowledge Driven FunctionalSimulation Verilog Unified Simulation Libraries Implementation Tools Verilog-XL

Optional Concept Unified Schematic Libraries Symbol Body LogiCores Non-schematic block: EDIF, XNF or NGO Genview module.v LogiBLOX Verilog module.ngo FunctionalSimulation Verilog-XL ConstraintsFile EDIF, XNF, or NGO EDIF TimingSimulation Testfixture Verilog Simprim Library Knowledge Driven Verilog Verilog-XL SDF Implementation Tools Pin - netlister from Cadence Generic Mixed Mode Flow Schematic Entry CONCEPT Via HDL_Direct NGD2VER CONCEPT2XIL NGDBuild Board-level Simulation XIL2CDS

.xnf .edf .ngo K nowledge-Driven .ngd Implementation .ncd routed.ncd routed.nga routed.bit Xilinx Implementation Flow NGDBuild To Simprim-Based Functional Sim. NGD2VER MAP To Post-Map Timing Sim. NGD2VER To Post-Implementation Timing Simulation PAR To Design Download BITGEN NGDAnno

.nga Point Verification .tv .sdf .pin .v User-Specified Verilog Testbench Body Chips_prt Verilog Simprim Library - netlister from Cadence Timing Simulation (Verilog) -tf: Generate testfixture -ul: Include `uselib -pf: Generate pin file - (for board-level sim) NGD2VER -tf -ul -pf Edit XIL2CDS For Board-level Simulation TimingSimulation Verilog-XL

.nga Point Verification [ ] .tb .sdf .vhd Edit User-Specified VHDL Testbench TimingSimulation ** VHDL Simprim Library Leapfrog Timing Simulation (VHDL) -tb: Generate testfixture NGD2VHDL -tb ** This Library must be compiled by user

Synergy Synthesis Libraries Verilog Unified Simulation Libraries Concept Unified Schematic Libraries Verilog Verilog FunctionalSimulation Verilog-XL EDIF Testfixture Knowledge Driven Verilog Verilog Simprim Library SDF Implementation Tools Pin - netlister from Cadence Flow Summary HDL Entry Schematic Entry CONCEPT SYNERGY Concept2XIL VLOG2XIL Concept2XIL -sim_only TimingSimulation Verilog-XL Board-level Simulation XIL2CDS

Cadence Methodology Changes • Cadence 5.X Environment • lib/cell/view/file structure • PIC flow • Verilog as intermediate format • EDIF interface to Xilinx • Standard HDL Direct methodology

XACT to M1 Migration • ITERATED INSTANCES instead of SIZE property (See HDL Direct User Guide) • modify PATH property • Ex. PATH = I4 changes to PATH=I4(2:0) to indicate 3 copies of an object • SCALD to HDL Direct schematic conversion (REQUIRED) • X-BLOX to LogiBLOX conversion • all X-BLOX modules must be replaced with their LogiBLOX counterparts

PATH = I4(2:0) PATH = I4 D Q D Q 3 instances XACT to M1 Migration • Iterated Instances instead of SIZE property • Ex. Set PATH = I4(2:0) to indicate 3 copies of an object with PATH value of I4

ctrl<2..0> ctrl<2> ctrl<1> ctrl<0> XACT to M1 Migration • Tapping Bus Bits • renaming of bits not allowed ctrl<2..0> ctrl2 ctrl1 ctrl0 **** WRONG! **** (bits renamed, alias_bit error) CORRECT

XACT to M1 Migration • Other “GOTCHA’s”: • MERGE bodies--all nets must be named • Name of each design subblock must match the corresponding SCALD directory name ctrl<2> ctrl<2..0> ctrl<1> ctrl<0>

X-BLOX to LogiBLOX Conversion • Recommended method: Replace all X-BLOX components with LogiBLOX modules • Generate LogiBLOX module • .v (gate level netlist for simulation only) • .NGO (for implementation) • Verilog template (for instantiation in Verilog) • Create symbol body (schematics only) • genview in Concept • Add: parameter cds_action=“ignore”; • Instantiate module in your design

Integrating LogiBLOX modules • Run LogiBLOX standalone: • lbgui (select “cadence” as vendor) • Generate symbol body from .v file • genview-i <module.v> -v logic body verilog • Add line to block/logic/verilog.v module: • parametercds_action = “ignore”; • Copy .ngo file to Xilinx run directory • (xilinx.run, by default)

X-BLOX to LogiBLOX Conversion • Alternate Method (short-term solution only) • Process design in XACT down to .XTF • Use .XTF as input to M1 Core tools • Disadvantages • No support for new architecture features • No support for XNF format will be available in future M1.5 release

New Libraries • M1 Concept Unified Library • M1 Verilog Unified Library • M1 SIMPRIM Verilog Library • M1 Synergy Libraries (available from Cadence only) • No Composer support

New Libraries • Concept Unified • $XILINX/cadence/data/xce<family> (e.g. xce4000ex) • No support for SIZE property • use Iterated Instances • compatible with pre-M1 Concept Unified libraries • shape and size of symbols • pin locations • component and pin names

New Libraries • Verilog Unified simulation library • $XILINX/cadence/data/ verilogxce______ (e.g., verilogxce4000ex) • for HDL Directfunctional simulation only • no timing checks

New Libraries • SIMPRIM Verilog libraries • included as part of Xilinx M1 Core • generic, architecture-independent • located in $XILINX/verilog/data

New Libraries • SIMPRIM Verilog libraries • support all post-NGDBUILD simulation • post-NGDBUILD (functional, gate-level) • post-MAP timing (optional) • post-PAR (post-route) timing • library primitive naming system • X_FF.vmd (flip-flop) • X_BUF.vmd (buffer)

Concept Setup Files • master.local • design.wrk • global.cmd • cds.lib • startup.concept

master.local • points to location of Xilinx Concept libraries file_type = master_library; “xce4000ex” ‘/tools/xilinx/cadence/data/xce4000ex/xce4000ex.lib’; “xce4000e” ‘/tools/xilinx/cadence/data/xce4000e/xce4000e.lib’; “xce5200” ‘/tools/xilinx/cadence/data/xce5200/xce5200.lib’; “xce3000” ‘/tools/xilinx/cadence/data/xce3000/xc3000.lib’; “xce7000” ‘/tools/xilinx/cadence/data/xce7000/xce7000.lib’; “xce9500” ‘/tools/xilinx/cadence/data/xce9500/xce9500.lib’; end. *Note: XC5200 and XC3000 architectures are not supported in the M1.3 core tools

design.wrk • Concept project library file FILE_TYPE = LOGIC_DIR; "UNNAMED" 'unnamed'; "MYBLOCK" 'myblock'; END.

cds.lib • Concept 5.x library file define xce4000ex_syn /tools/xilinx/cadence/data/xce4000ex_syn define xce4000e_syn /tools/xilinx/cadence/data/xce4000e_syn define xce5200_syn / tools/xilinx/cadence/data/xce5200_syn define xce3000_syn /tools/xilinx/cadence/data/xce3000_syn define xce7000_syn /tools/xilinx/cadence/data/xce7000_syn define xce9000_syn /tools/xilinx/cadence/data/xce9000_syn *Note: XC5200 and XC3000 architectures are not supported in the M1.3 core tools

global.cmd • Concept project library alias file master_library "./master.local" ; library "xce4000ex" , "hdl_direct_lib", "xcepads", "standard" ; use "design.wrk" ; root_drawing "unnamed" ;

startup.concept (reinforces HDL Direct naming conventions) set hdl_direct on set hdl_checks on set check_signames on set check_net_names_hdl_ok on set check_port_names_hdl_ok on set check_symbol_names_hdl_ok on set capslock_off *(preserves case, may be important for TIMESPECs) runopl /products/cds.ver97a/tools/fet/concept/hdl_direct /bin/autosym

Concept Properties • Properties are specified as: name=value • Usexilinx.pffin $XILINX/cadence/data as a guide to property specification format • Boolean • must be set to TRUE or FALSE • Example: FAST=TRUE (output slew rate) • KEEP=TRUE (“X” in XACT) • Normal • Location constraints (LOC=P6) • Timegrps (GRP01=mygrp) • (names are case-sensitive if you specify “set caps_lock_off” in startup.concept)

CONFIG PART=XC4028EX-3-PG299 Concept Properties • Part type property • “PART=XC4028EX-3-PG299” • Attach toCONFIG symbol:

Global signal support in M1.2/M1.3 • M1.2.11: • glbl.v contains declarations of global wires in “glbl” module • signals referenced as glbl.gsr, glbl.gts, etc. • M1.3.x: • Verilog macros in the test fixture assign the names of the global signals • `define GSR_SIGNAL sig_name

Global signals in M1.2 • M1.2.11 • module glbl in separate glbl.v file • global signals declared as wires: • wire gsr; // 4k • wire gts; // 4k, 5k* • wire prld; // 7k, 9k • wire gr; // 3k*, 5k* * 3K and 5K not supported in M1.3 core tools • pre-route HDL Direct simulation netlist: X_FF inst_name2 (.IN … .RST(glbl.gsr));

Global signals in M1.2 • post-NGDBUILD simulation: • glbl.gsr OR’d with local reset: X_OR2 inst_name1 (.IN0(glbl.gsr),.IN1(local_clr), .out(xxxx.GSR.OR)); X_FF inst_name2 (.IN(aaaa), .CLK(bbbb), .CE(cccc), .SET(ssss) … .RST(xxxx.GSR.OR)); • Testbench: • force glbl.gsr = 1;

Global signals in M1.2 • Verilog-XL command line: verilog design.tv design.v glbl.v * glbl.v not supported in M1.3

Global signals in M1.3 • Utilizes Verilog macros* • Unified Verilog library modifications to support the Verilog macros • Test fixture support *Verilog macro: `define xx_SIGNAL where “xx” = GSR, GR, GTS, or PRLD

Global signals in M1.3--LIBRARIES • Global Reset support (4K) • Each 4K Verilog Unified library register model contains the following block of code to model GSR: `ifdef GSR_SIGNAL wire GSR = `GSR_SIGNAL; `else wire GSR; `endif