The Field-Effect Transistor

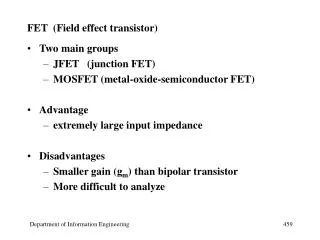

The Field-Effect Transistor. Preview MOS field-effect transistor MOSFET DC circuit analysis Basic MOSFET application: Switch, digital logic gate, and amplifier Junction field-effect transistor. Preview. 兩種場效電晶體 MOSFET( 金氧半 ) 引發第二次電子革命,使高密度 VLSI 可行

The Field-Effect Transistor

E N D

Presentation Transcript

The Field-Effect Transistor • Preview • MOS field-effect transistor • MOSFET DC circuit analysis • Basic MOSFET application: Switch, digital logic gate, and amplifier • Junction field-effect transistor

Preview • 兩種場效電晶體 • MOSFET(金氧半) • 引發第二次電子革命,使高密度VLSI可行 • 本章內容:物理結構及運作、電流-電壓特性、DC分析、應用(切換開關、數位邏輯、線性放大器) • 可取代電阻,所以可設計電路僅含MOSFET • JFET(接面) • 若是pn接面則為pn JFET • 若是蕭基接面則為金屬半導體FET (MESFET) • 使用在高速高頻之應用,如微波放大器

MOS field-effect transistor (1/21) • 前言 • 70年代變實際,比起BJT,可以做的很小 • 數位電路可以只含MOSFET,不用電阻及二極體,所以可以製成高密度VLSI • 電流由垂直於半導體表面及電流之電場控制 • 場效:藉由外加垂直於表面的電場,用以調變半導體導電度或控制電流的現象 • 同樣地,基本電晶體原則為兩端子間電壓控制另一端子之電流

MOS field-effect transistor (2/21) • Two-terminal MOS structure • MOSFET之核心:金屬-氧化物-半導體電容 • 金屬:鋁或其他金屬,很多是用高導的多晶矽 • 氧化層:厚度tox,介電常數ox • 平行板電容輔助說明 • C= A/d,A為平板面積,d平板間距 • p型半導體基板之MOS電容 • 金屬端稱為閘極,存有負電荷,如同平板電容頂板 • 電場透過半導體,電洞受力往氧-半界面。平衡時氧-半接面有電洞纍積層,如同平板電容之底板

MOS field-effect transistor (3/21) • 外加電壓極性反向 • 頂端金屬板存有正電荷 • 電場由上而下迫使電洞遠離氧-半接面而形成負的空乏電荷區 • 電壓再加大,少數載子被引至接面而形成電子反轉層 • n型半導體基板之MOS電容:與p型類似 • 但其中為電洞反轉層

MOS field-effect transistor (4/21) • 增強型:指需有外加電壓才會有反轉層 • p型基板:需正閘極電壓以產生電子反轉層 • n型基板:需負閘極電壓以產生電洞反轉層 • n-channel enhancement-mode MOSFET • 電晶體結構 • 除同MOS電容之閘極、氧化層及p型基板區外,尚有兩個n-區稱為源極及汲極 • 電流來自於反轉層(或稱通道區)之電荷流動 • 通道長度L及寬度W小於1 m,氣化層厚度約在400 埃(Å=10-8 cm=10-10 m) • 場氧化層:鋪在外面以接金屬連線之厚氧化層 • 閘極材料常為高摻雜之多晶矽

MOS field-effect transistor (5/21) • 基本電晶體運作 • 閘極零偏壓時:源極與汲極被p區隔開如同二個背對背之二極體,無電流產生 • 閘極加上一個夠大的正電壓:氧-半接面處有電子反轉層以連接n-S及n-D,所以源極及汲極間有電流產生 • n-通道增強型MOSFET(增強型NMOS電晶體) • 因需外加電壓以產生反轉電荷故稱增強型 • 因反轉層之電荷為電子故稱n-通道 • NMOS電晶體:D-S間外加電壓則源極提供電子流向汲極,電流則是由汲極流向源極 • 電流大小視反轉層電荷而定,即依外加閘極電壓而定 • 閘極由絕緣之氧化層隔開故無閘極電流 • 通道與基板由空間電荷區隔開所以基極亦無電流流過

MOS field-effect transistor (6/21) • Ideal MOSFET current voltage characteristics • NMOS電晶體之門檻電壓VTN • 即外加閘極電壓以產生與基板多數載子相同密度之反轉電荷,可想成打開電晶體之門檻電壓 • 對增強型而言為正的,如此才可以產生反轉電荷 • 若閘極電壓小於門檻電壓則無電流 • 一般閘極及汲極電壓之測量是相對於源極 • 圖之基板及源極接地,G-S電壓小於VTN,D-S有一小電壓 • 無反轉層產生且D-基板之pn接面反偏,所以無汲極電流

MOS field-effect transistor (7/21) • 若閘極電壓大於門檻電壓且D-S有外加電壓則有電流 • G-S電壓大於VTN有反轉層產生,若D-S有一小電壓則反轉層電子由S到D,即D極電流由D流入經通道至S再流出電晶體 • 正的D極電壓使D-基板之pn接面反偏,所以電流流經通道區而非經pn接面 • 在小的vDS時,iD對vDS特性曲線 • vGS<VTN時無D極電流,vGS>VTN則有且隨vGS增大而增大,因閘極電壓愈大則反轉電荷密度愈大所以有較大之D極電流 • 在小的vDS時,反轉電荷密度在通道內皆一致,D極電流隨vDS增加而增加

MOS field-effect transistor (8/21) • 增加vDS即D極電壓增加 • 近D極端跨在氧化層之壓降減少誘發之反轉電荷密度減小通道之增量電導降低D極電流增加變緩 • 飽和電壓vDS(sat)= vGS-VTN • 當增加vDS使得在D極跨在氧化層之壓降恰等於VTN時,在D極誘發之反轉電荷密度為零,通道之增量電導為零,iD對vDS之斜率為零 • vGS-vDS(sat)= VTN:可想成VTN= vGD(sat) • vDS>vDS(sat)則反轉電荷之零點往S極移動 • 由S極進入之電子經通道往D極,到達零電荷點注入空間電荷區再由電場掃至D接點,類似雙極電晶體反偏B-C接面掃出電子之程序 • 飽和區:理想MOSFET有固定之D極電流 • BJT之飽和指C極電流不再隨B極電流增加且vCE到達最小值,MOSFET(在某固定vGS)則指電流達到最大不再隨vDS改變

MOS field-effect transistor (9/21) • iD對vDS的關係式 • vGS增加則iD對vDS的起始斜率增加,且vDS(sat)增加(如圖虛線) • vDS<vDS(sat)為非飽和(三極)區: • vDS>vDS(sat)為飽和區: • 理想上,增量(小訊號)電阻為無限大 • 因iD與vDS無關 • 導電參數 , n為反轉層電子之動性 • 氧化層單位面積電容 • 矽元件ox=(3.9)(8.8510-14) F/cm=0.34515 nF/cm(=10-10 F/m) • 導電參數為電子與幾何參數之函數,一般n及Cox(即 )視為常數,所以W/L為設計參數用以產生特定之I-V特性曲線

MOS field-effect transistor (10/21) • Example 5.1:求n-通道MOSFET之電流 • 先求導電參數Kn(單位為A/V2)再代入電流公式 • Circuit symbols and conventions • n-通道MOSFET的慣用電路符號 • 垂直實線表閘極,虛線表通道,之間為氧化層 • 虛線亦表其為增強模式 • 本體或基板端子之箭頭表基板與通道間pn接面之極性,此方向亦表明電晶體之類型 • 箭頭由基板往通道,所以是n通道元件 • 本書多數應用隱含假設源極與基板相接一起 • 所以隱去基板端而得簡易電路符號 • 在源極之箭頭表電流方向(p進,n出), 如此便可不用標源極及汲極

MOS field-effect transistor (11/21) • Additional MOSFET structures and circuit symbols • n-通道空乏型MOSFET • 剖面圖與外加閘極電壓 • 閘極無電壓時,在氧化層下有n-通道區(反轉層),來自製造時雜質之引入 • 空乏型意味著在無閘極電壓仍有通道 • 需負的外加閘極電壓才能關掉n-通道空乏型MOSFET • 外加負的G-S電壓 • 誘發空間電荷區在氧化層下n-通道區厚度減少通道導電度減少D極電流減小 • 閘極電壓=門檻電壓(負的):空間電荷區與n-通道區完全重疊,電流為零 • 正的G-S電壓:產生電子纍積層而增加D極電流

空乏型 MOS field-effect transistor (12/21) • 電流-電壓特性:與增強型同 • VTN在增強型為正,在空乏型為負 • 電路符號 • 垂直實線代表空乏型 • 在增強型垂直線為虛線 • 簡化的符號 • 在S極的箭頭依然代表電流方向,n-通道為流出 • 厚實線代表空乏型 • p-通道MOSFETs (PMOS電晶體) • 雜質與n通道元件相反,所以門檻電壓VTP在增強型為負,空乏型為正 • 運作與n-通道元件相同,只是電荷載子為電洞而非電子,所以電流方向及電壓極性相反 • 非飽和區的i-v關係: 增強型

MOS field-effect transistor (13/21) • 飽和區 的i-v關係: • 導電參數 • p為反轉層電洞之動性 • Example 5.2: p-通道空乏型飽和區電流 • 直接代公式,再驗證真的vSD> vSD(sat) • 電路符號:與n-通道類似,箭頭方向不同,表電流由源極流入電晶體 • 互補式MOSFETs (CMOS) • 在同一電路上使用n-通道及p-通道元件 • 為了使n -通道及p-通道元件電氣上等效 • 門檻電壓相等及導電常數相等(調整W/L) 增強型 空乏型

MOS field-effect transistor (14/21) • Summary of transistor operation • VTN或VTP可看成D-G所形成之電位障(VD-VG) • VGD恰抵銷此電位障則剛好通與不通之間 • n-通道:增強型VTN>0,空乏型VTN<0,皆VGS> VTN則通 • p-通道:增強型VTP<0,空乏型VTP>0,皆VSG >-VTP則通, • D-S飽和電壓:一定大於等於0 • 隨vGS(vSG)而變,將VGD(sat)想成門檻電壓 • n-通道:vDS(sat) =VDG(sat)+vGS=-VGD(sat)+vGS =vGS-VTN • p-通道:vSD(sat) =vSG+VGD(sat)=vSG+VTP

MOS field-effect transistor (15/21) • 記法 • 門檻電壓之正負 • 由原電性來記:增強型需外加電力才通,空乏型原本就通 • n通道之反轉電荷為負,所以在增強型需外加正電壓以吸引負電荷才通,空乏型需外加負電壓以斥走負電荷才不通 • p通道之反轉電荷為正,所以在增強型需外加負電壓以吸引正電荷才通,空乏型需外加正電壓以斥走正電荷才不通 • 輔助記法XOR(同性相斥為正、異性相吸負) • n(通道)記為負,p(通道)記為正;增強型記為正,空乏型記為負。例n通道增強型表為負正,取XOR得正 • 導通之條件:VGD(sat)想成門檻電壓配合飽和電壓>0 • n通道: vDS(sat)=vGS-VTN>0vGS>VTN • p通道: vSD(sat) =vSG+VTP>0vSG>-VTP

MOS field-effect transistor (17/21) • Nonideal current-voltage characteristics • 有限輸出阻抗 • 理想上在飽和時iD與vDS無關,但實際上在I-V特性曲線過飽和點後仍有非零之斜率存在 • 通道長度調變:飽和時,反轉電荷為零的點在通道中是會遠離D極而使有效通道長度變短之現象 • I-V特性曲線放大如圖 • 外插之點同雙極電晶體之Early電壓 • I-V關係變為 • iD=0時 • 通道長度調變所引起的輸出電阻

MOS field-effect transistor (18/21) • 本體效益 • 直到目前皆假設基板(或本體)接至源極,如此門檻電壓是固定的 • 積體電路內所有n-通道MOSFET的基體通常是共用的,且連至電路的最負電位 • 如圖為兩個n-通道MOSFET串聯 • p-型基體共用 • M1的D極與M2的S極共用 • 當兩電晶體導通,M1之D-S電壓非零,即M2之S極與基體非等電位 • 本體效益: S極-本體接面有零或反偏電壓且電壓改變會改變門檻電壓 • 相同狀況也存在p-通道元件

MOS field-effect transistor (19/21) • 門檻電壓: • 為使S極-本體接面有零或反偏電壓,需 • VTN0為 時之門檻電壓 • 稱為截止門檻或本體效應參數與元件特性有關約在 • 半導體參數約在0.35V與摻雜有關。 • n-通道元件之門檻電壓因本體效應而增加 • 本體效應會改變門檻電壓而降低電路效能,本書為簡化而暫忽略本體效應 • 次門檻導電:理想上在飽和 (如圖) • 實際上當 略低於 時仍有電流,稱為次門檻電流 • 對單一元件此效應不明顯,但若是在積體電路內數千數百個元件皆偏壓在略低於門檻電壓,則將由明顯之功率消耗 • 本書將不特別考量次門檻電流。但在電路中為使MOSFET關閉,正常的設計應使元件偏壓在低於門檻電壓十分之幾伏才能使元件真的關閉

MOS field-effect transistor (20/21) • 崩潰效應 • D極-基板pn接面:當D極電壓太大且有雪崩乘積,如同二極體反偏使pn接面崩潰一樣 • 鑿穿崩潰:當元件變小時此種崩潰機制變得明顯 • 當D極電壓夠大使得D極附近的空乏區完全穿過通道而到S極,這效應亦使D極電流迅速增加只要小量D極電壓的增加 • 近雪崩或回奪崩潰:源於MOSFET之二次效應 • S-基板-D結構等效於雙極電晶體,當元件變小,寄生雙極電晶體隨D極電壓增大而起作用,也增強了崩潰效應 • 當氧化層內的電場變得夠大,氧化層也會發生崩潰而產生致命的損壞 • 氧化矽的崩潰電壓約在 • 初步近似使用 :當 Å,崩潰電壓約為30V,但通常安全係數為3,所以安全的閘極電壓為10V

MOS field-effect transistor (21/21) • 安全界限是需要的,因氧化層的缺陷會使崩潰電場降低 • 閘極輸入阻抗很高,一小量的閘極靜電荷將導致崩潰電壓的超過。為避免靜電荷在閘極電容累積,MOS IC的輸入通常包含一個閘極保護元件如反偏二極體 • 溫度效應 • 門檻電壓VTN及導電參數Kn為溫度之函數 • 門檻電壓大小隨溫度而降低 • 即在給定一VGS時,D極電流隨溫度而增加 • 導電參數為反轉層載子移動性的函數 • 移動性隨溫度升高而降低 • 給定一VGS,溫度增加的靜效應為D極電流降低 • 因移動性的溫度相依性大於門檻電壓的 • 此特殊結果在功率MOSFET有一負回饋的情況 • Kn下降本質上限制通道電流也提供了穩定性

MOSFET DC circuit analysis (1/13) • 前言 • 以下開始分析設計dc偏壓的MOS電晶體電路 • 為設計MOSFET放大器的重要部分 • 本章很多電路之電阻與MOS電晶體串聯,但實際的MOSFET IC,電阻是以其他MOSFET所取代,所以電路完全由MOS元件所構成 • Common-Source circuit • 如圖之NMOS增強型 • S極接地,與輸入輸出的部分相同 • 耦合電容對dc為開路,但允許訊號耦合至閘極

MOSFET DC circuit analysis (2/13) • dc等效電路及分析 • 假設VG>VTN且在飽和區 • D極電流 • D-S電壓 • 若>VDS(sat)=VGS-VTN則分析正確 • 若<VDS(sat)則電晶體偏壓在非飽和區 • D極電流改以非飽和公式求 • Example 5.3:D極電流及D-S電壓 • VGS=VGIDVDS • VDS>VDS(sat)所以正確

MOSFET DC circuit analysis (3/13) • PMOS增強型 • S極接至+VDD,在ac等效電路即訊號之接地 • 分析與NMOS同 • , • 假設VGS<VTP或VSG>|VTP|及在飽和區 • , • 若VSD>VSD(sat)=VSG+VTP則正確 • 若VSD<VSD(sat) 則在非飽和區 • Example 5.4: D極電流及S-D電壓 • VGVSG,假設飽和求IDVSD<VSD(sat),改用非飽和求IDVSD<VSD(sat),所以正確 • 當線性放大器,電晶體是偏壓在飽和區

MOSFET DC circuit analysis (4/13) • Load line and mode of operation • 負載線可幫助觀看MOSFET偏壓在那一區 • 同上之共源極電路 • 由D-S迴路可得負載線等式 • VDS=VDD-IDRD • 兩端點在ID=0及VDS=0 • Q點:負載線與特性曲線交點 • D極dc電流及D-S之dc電壓 • VGS<VTN:D極電流為0,電晶體為關閉 • VGS恰大於VTN:電晶體導通且偏壓在飽和區 • VGS增加,則Q點沿負載線上移,超過過渡點則進入非飽和區 • 過渡點:飽和與非飽和區之邊界VDS=VDS(sat)=VGS-VTN

MOSFET DC circuit analysis (5/13) • Example 5.5:求共源極之過渡點 • 即某VGS下之VDS(sat)= VDS=VDD-IDRD=VDD-Kn[VDS(sat)]2RDVDS(VGS) • 若外加VGS小於此VGS則在飽和區,反之,則在非飽和區 • 解題技巧:MOSFET直流分析 • 假設偏壓在飽和區, VGS>VTN、ID>0、VDS VDS(sat) • 使用飽和時I-V的關係分析電路 • 評估第一步假設是否正確。若VGS<VTN則電晶體可能關閉。若VDS<VDS(sat)則電晶體可能偏壓在非飽和區 • 若起初假設驗證錯誤則重新假設及分析,重複第三步

MOSFET DC circuit analysis (6/13) • Common MOSFET configurations: DC analysis • Example 5.6:設計dc偏壓以產生特定D極電流 • 假設飽和由公式得VGSVG=VS+VGS、I R1+R2R2R1驗證VDS>VDS(sat) • 在雙極電晶體使用射極電阻使Q點穩定,在MOSFET可使用S極電阻 • 因製成關係通道長寬、氧化層厚度、載子動性及門檻電壓皆會隨元件不同而有所不同 • S極電阻常以定電流源取代,定電流與電晶體參數無關因而穩定電晶體

MOSFET DC circuit analysis (7/13) • Example 5.7:MOSFET電路以定電流偏壓 • 已知VD,由歐姆定律RD • 驗證:假設飽和公式得VGSVSVDS>VDS(sat) • 增強式負載元件:非線性電阻 • 因為是增強型元件,所以VTN>0 • 則一定在飽和區,因為vDS=vGS>vDS(sat)=vGS-VTN • I-V關係: • 無論n通道或p通道,此負載元件皆在飽和區

MOSFET DC circuit analysis (8/13) • Example 5.8:增強型負載元件之特性 • 利用飽和公式及 (ID表為VGS)VGS(取正數,因飽和需VGS >VTN)ID(亦可先求IDVGS) • 此種電路非放大器,但常為有效的負載電阻 • 將增強型負載元件連至另一MOSFET • 形成放大器或數位電路的反相器 • 負載元件ML總在飽和區 • 驅動電晶體MD則可能在飽和或非飽和區 • 視輸入而定 • Example 5.9:含增強型負載元件之電晶體dc電流電壓 • 求輸入5V及1.5V時之輸出

MOSFET DC circuit analysis (9/13) • VI=5V:輸入大VGSD大VDSD較不易大於VDSD(sat)易非飽和 • 表為VDD、VI及VOVO=7.65或0.349(取0.349,因不可大於VDD) • 驗證MD在非飽和區: (ID) • VI=1.5V:輸入小VGSD小VDSD較易大於VDSD(sat)易飽和 • 表為VDD、 VI及VOVO=2.88 • 驗證MD在飽和區: (ID) • 電腦模擬 • VI1:電晶體關閉,IDL=0VO =VDD-VGSL =VDD-VTNL =4 • 1<VI<2.25:電晶體在飽和區,VO為VI之線性函數 • 2.25<VI:電晶體在非飽和區,VO為VI之非線性函數

MOSFET DC circuit analysis (10/13) • 驅動電晶體之過渡點:此時VDSD(sat)=VGSD-VTND • 使用 • 空乏型負載元件:G-S連接在一起 • 因空乏型的門檻電壓是負的,所以vDS(sat)為正 • 可偏壓在飽和或非飽和區,端視電晶體參數、VDD及RS而定 • Example 5.10:含空乏型負載元件之電路 • 假設飽和ID驗證VDS>VDS(sat)

MOSFET DC circuit analysis (11/13) • 將空乏型負載元件連至另一MOSFET • 形成放大器或數位電路的反相器 • 負載元件ML及驅動電晶體MD皆可能在飽和或非飽和區,視輸入而定 • Example 5.11:電路含空乏型負載元件之dc電流電壓 • VI=5V:輸入大VGSD大VDSD較不易大於VDSD(sat)假設非飽和 • VO=7.90或0.1(取0.1,因不可大於VDD)(ID) • 驗證MD在非飽和區及ML在飽和區

MOSFET DC circuit analysis (12/13) • 電腦模擬 • VI1:皆關閉,VO=VDD=5 • 1<VI<約1.9:驅動器在飽和區,負載在非飽和區 • VI約1.9:皆在飽和區 • 若假設=0,則在過渡區時,輸入電壓幾乎無變化 • VI>約1.9:驅動器在非飽和,負載在飽和 • CMOS(互補式MOS) • 互補指在電路上n-通道及p-通道的電晶體皆有 • 應用在類比與數位電路皆相當廣泛 • 一個CMOS反相器: • NMOS當驅動器,PMOS當主動負載 • 另一種接法:兩個閘級接在一起當輸入 • 兩個電晶體皆可在飽和或非飽和 • Example 5.12:模擬CMOS反相器特性 • PMOS之VSG=0.75,PMOS D極看入之有效電阻很大

MOSFET DC circuit analysis (13/13) • Constant-Current source biasing • 優點:D極電流與電晶體參數無關 • 組態及推導 • M2、M3及M4形成電流源 • M3及M4連接成二極體之組態所以在飽和區,並建立參考電流 • M2則假設在飽和區,以M3之G-S電壓為輸入建立偏壓電流IQ • Example 5.13:MOSFET定電流源的電流電壓 • 如上求法再驗證M2在飽和區

Basic MOSFET application: Switch,digital logic gate, and amplifier (1/4) • 前言 • 應用:切換電流、電壓及功率;執行數位邏輯功能;放大小的時變訊號 • NMOS inverter • 電晶體當開關比機械式的開關快且可靠 • 本節考慮一個稱為反相器的開關 • 另兩個開關組態:NMOS傳輸閘、CMOS傳輸閘 • n-通道增加型MOSFET反相器 • vI<VTN:電晶體關閉,iD=0、vO=VDD、無功率消耗 • vI>VTN:電晶體導通 • 起初在飽和區:因vGS =vI尚小,所以vDS>vGS-VTN

Basic MOSFET application: Switch,digital logic gate, and amplifier (2/4) • vI增加:則vDS降低(因vGS增加使iD增加,VRD也增加),變至非飽和區 • vI=VDD:vO得最小值,iD得最大值 • Example 5.14:設計功率MOSFET之大小以符合特定規格 • 負載為電磁圈,需最小電流為0.5A,其有效負載電阻8-10 • 為使電流與負載無關,所以假設電晶體在飽和區 • 需VDS>VDS(sat)=VGS-VTN,即VGS<VDS(min)+VTN • 因VDS(min)=VPS-VR(max) =10-0.5R(max) =5,可取VGS=5 • 利用飽和公式W/L及P(max)=VDS(max)ID • 吾人可發現,無輸入電流卻有很大的輸出電流。另這種尺寸是需要用功率電晶體

Basic MOSFET application: Switch, digital logic gate, and amplifier (/4) • Digital logic gate • 電晶體反相器:0為低,VDD為高 • 低輸入:電晶體關閉,輸出為高 • 高輸入:電晶體非飽和,輸出為低 • 雙輸入NOR • Example 5.15:電流電壓 • 輸入皆低:皆關閉,輸出為高 • 輸入一高一低:低者關閉,高者非飽和,利用非飽和公式求VO,再求高者電流 • 輸入皆高:皆非飽和,利用KCL及非飽公式求VO,再求各電流

Basic MOSFET application: Switch, digital logic gate, and amplifier (4/4) • MOSFET small signal amplifier • 連接其他電路元件以放大小的時變訊號 • 共源極電路 • 設計偏壓電阻之比例以建立特定的Q點 • 弦波輸入則G-S間電壓有弦波訊號疊加在dc靜態值上,所以Q點會上下移動 • D極電流及D-S間電壓亦隨之上下移動 • 輸出訊號比輸入大,所以是放大,訊號增益則依電晶體參數及電路元件值而定 • 下章將發展放大器之等效電路

Junction field-effect transistor (1/10) • 前言 • 兩類一般的接面FET:pn接面FET (pn JFET);金屬半導體FET (MESFET)使用蕭基位障接面 • 運作 • 電流流經稱為通道之半導體區,兩端為歐姆接點 • 基本動作:垂直於通道之電場調變通道之導電度 • 因為電場是誘發在反偏pn接面或蕭基位障接面之空乏區,所以為閘極電壓之函數 • 因此藉由閘極電壓調整通道導電度進而調變通道電流 • JFET比MOSFET早發展但反較少應用使用,因 • G與D電壓極性在MOSFET相同,但在JFET常相反 • 所以JFET只用在特殊應用,在此討論較少

Junction field-effect transistor (2/10) • pn JFET and MESFET operation • pn JFT • 為多數載子元件:與BJT不同 • 圖為n通道pn JFET:n區通道在兩p區間,主要載子(電子)由S流至D,兩G極連成單一G極 • p通道pn JFET之p區、n區與n通道的相反,電洞由S流至D,所以電流與電壓極性亦與n通道相反 • 較n通道更常用在低頻元件,因電洞移動性較低 • 閘極外加電壓(以n通道pn JFET為例) • vG=0、vS=0、vD小正:有iD,因n通道本質上為電阻,所以iD對vDS在小vDS時為線性 • 若外加閘極電壓非零,則通道之導電度改變

Junction field-effect transistor (3/10) • 負閘極電壓:G-通道為反偏,空間電荷區變寬,通道變窄,通道電阻變大,所以iD對vDS在小vDS時斜率變小 • 較大的負閘極電壓:空間電荷區完全佔滿整個通道,此情況稱為夾止(pinchoff)。因空乏層隔離S與D,所以iD=0 • 通道電流由閘極電壓控制,即元件某部分之電流由另一部分之電壓控制,此即基本電晶體動作 • 空乏型元件:pn JFET一般是導通的 • 需有外加電壓到閘極才能將電晶體關閉

Junction field-effect transistor (4/10) • vG=0,D極的電壓改變 • 當D極電壓往正的增加 • 在D極附近之G-通道接面變成反偏,空間電荷區加大,通道變小,通道有效電阻增加, iD對vDS的特性變小 • 有效通道電阻沿著通道改變,因電流是固定,所以壓降也沿著通道改變 • 再進一步增加,則在D端發生夾止,剛夾止之電壓即vDS(sat) • 夾止點後再如何增加D極電壓皆無法增加D極電流 • 飽和區:vDS>vDS(sat) ,iD理想上與vDS無關

Junction field-effect transistor (5/10) • MESFET • 閘極為蕭基位障接面而非pn接面 • 雖可用矽製作,但一般使用砷化鎵或其他複合半導體材料 • 如圖,薄的砷化鎵磊晶層做成主動區,基板則為高電阻之砷化鎵物質,稱為半絕緣基板 • 優點:砷化鎵有較高之電子移動性,所以過渡時間較短反應較快;半絕緣基板使寄生電容降低及製程簡單 • 電場效應 • 反偏G-S電壓在金屬閘極下引發一個空間電荷區會調變通道導電度,如同pn JFET • 若外加負電壓夠大則空間電荷區將達到基板而發生夾止 • 如圖為一空乏型元件,需外加閘極電壓才會夾止而關閉

Junction field-effect transistor (6/10) • 另一型MESFET—增加型 • 通道是夾止的,即使vGS=0 • 這種MESFET通道厚度小於零偏壓之空間電荷區之寬度,為打開通道需使空乏區減小,即需外加一個順偏在G-半導體接面,當輕微順偏使空乏區恰延伸為通道寬度 • 門檻電壓:產生夾止情況之G-S電壓,對n通道增加型為正,與n通道空乏型之負門檻電壓不同 • 施加較大的順偏則使通道打開,但需限在十分之幾伏以免有明顯之閘極電流 • 上圖為n通道增加型MESFET,亦有p通道增加型MESFET • 優點:可使G與D之電壓極性相同 • 但這種元件輸出電壓之擺幅很小

n通道 p通道 n通道 p通道 n通道 p通道 Junction field-effect transistor (7/10) • Current-Voltage characteristics • JFET飽和區: • IDSS為vGS=0時之飽和電流,VP為夾止電壓 • n通道: VP為負, vGS常為負,vGS/VP為正 • 飽和區: • p通道: VP為正, vGS常為正,vGS/VP為正 • 飽和區:

Junction field-effect transistor (8/10) • Example 5.16:求iD及vDS(sat) • 給IDSS與VP及某些vGS公式 iD及vDS(sat) • JFET之電流量可藉IDSS (電晶體寬度之函數)而增加 • iD對vDS之斜率過飽和點可能非零,如同MOSFET • 電流 ,-1如同BJT之VA • 輸出電阻 • 增加型GaAs MESFET之i-v可被製成很像MOSFET • 理想增加型MESFET在飽和區 • 理想增加型MESFET在非飽和區 • Kn為導電度,VTH為門檻電壓等效於VP,對n通道增加型MESFET為正

Junction field-effect transistor (9/10) • Common JFET configurations: DC analysis • Example 5.17:n通道空乏型電路 • 已知Q點、假設飽和飽和公式求VGSVSRS及VDRD驗證飽和 • 為使電晶體偏壓在on,即使G及RS底端接地,VS皆需大於VG,所以使用RS來自我偏壓,使VS提高 • Example 5.18:分壓器偏壓電路 • Q點及RSRD;Q點、RS及假設飽和VS及VGSVGR2R1VDS驗證飽和 • JFET之dc分析與MOSFET同,皆假設G無電流

Junction field-effect transistor (10/10) • Example 5.19:p通道JFET之Q點 • ID=IQ及假設飽和VGSVS;ID=IQVDVSD驗證 • Example 5.17:增強型MESFET之設計 • 假設飽和VGSIDVDVSRSVGR2R1驗證 • 增強型MESFET之dc分析與MOSFET同,除G-S電壓需小於十分之幾伏外