GCT Leaf Card

GCT Leaf Card. 3/8/06. Presentation Structure. Overview This design should be familiar Block diagram Overall architecture Required and actual pin counts Hardware Issues LVDS FPGA implementation DDR FPGA implementation Clock tree Firmware Issues Overview Loading and control

GCT Leaf Card

E N D

Presentation Transcript

GCT Leaf Card 3/8/06

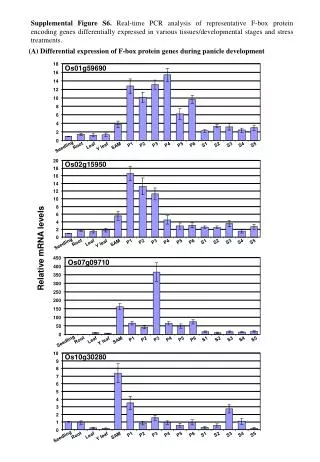

Presentation Structure • Overview • This design should be familiar • Block diagram • Overall architecture • Required and actual pin counts • Hardware Issues • LVDS FPGA implementation • DDR FPGA implementation • Clock tree • Firmware Issues Overview • Loading and control • Prototype code testing to date on hardware • SERDES code development on simulator • Signal Counts • Testing

Overview • Receives jet and electron data from RCT • 3 RCT crates per leaf card (jet) • 9 RCT crates per leaf card (electron) • RCT data presented on 1.6GHz optical links • Based on existing design • Double PMC • Dual Virtex2 4000/6000 • Discrete SERDES (2.4GHz TI TLK series) • Enhancements • Dual Virtex2Pro 70 • 16 integrated SERDES links per device • 3.2GHz maximum • 32 Optical inputs • 12 channel Agilent links • 2.5 GHz maximum • Retained features • Power supply • Phase controlled switchers • 30A at 1.5V, 15A at 2.5V • Basic layout • Decoupling scheme • .0201 cap pattern for FPGAs

Schedule • Schematic at Los Alamos • Initial review completed • Some minor modifications expected • SERDES/optical section • Signal integrity simulations in progress • Initial parts placement • Contract award imminent • Projected on March 15th • Transition funds in place • Covering current efforts • Delivery date of first two prototypes July 1st • Final review at end of May • Exact dates being worked out • Monthly progress reports will be generated • Submitted directly to CMS from engineering team

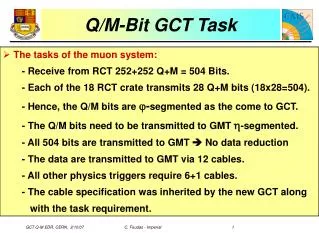

12 channel optical links 1.6Gbps links 12 links 4 links 4 links 12 links 120 pin LVDS link (60 pairs) 120 pin LVDS link (60 pairs) 4 links unused XC2VP70FF1513C XC2VP701513C Pre-clustered jets: 96 pins (48 pairs) 200 pins Pre-clustered jets: 96 pins (48 pairs) Et summary: 24 pins Readout: 10 pins Misc: 20 pins Finished jets: 54 pins Unfinished jets: 7 pins Finished jets: 54 pins Unfinished jets: 7 pins Energy summary: 24 pins Clock and control: 14 pins Readout: 20 pins Finished jets: 54 pins Unfinished jets: 7 pins P13 P11 P23 P21 P14 P12 P24 P22 Fully populated PMC I/O – 368 usable pins

Hardware issues, LVDS • Design makes extensive use of LVDS signaling • V2Pro supports true 100 Ohm termination • Much more efficient than V2 DCI • ~240mA for 60 pairs • Samtec QTS/H differential connectors • High density and speed • Commercial cable assemblies

Hardware Issues, DDR • DDR used for all single ended I/O • FPGA intercommunication at 40MHz • Use DCI (50 Ohm) or 6mA current limit • Less than 2A assuming 200 interconnects • Communication with Wheel card at 40MHz • Use DCI (50 Ohm) or 8-12mA current limit • 4.5A assuming 368, 12mA interconnects • Will be less • Board supports adhesive heat sinks • 5V fan headers if required

Clock Tree FPGA 1 Top/bottom die SERDES LVDS 1:4 fanout LVDS Oscillator FPGA 2 Top/bottom die SERDES LVDS 4x4 Crosspoint LVDS 1:4 fanout External COAX SMB FPGA 1 General Clocks PMC (40MHz) PMC (80MHz) LVDS 1:4 fanout FPGA control FPGA 1 General Clocks Skew = 2.5 nS max External COAX SMB Single ended clocks (2 per FPGA) tie directly to PMC

FPGA loading and control • JTAG • Single JTAG chain • 4 devices, 2 FPGAs and 2 FLASH PROMs • Jumper configurable • Local header or PMC via wheel card • Default configuration via Xilinx FLASH PROM • Single platform FLASH XCF32P per device • Control via wheel card (PMC) • USB test fixture for stand alone operation • No interface protocol defined by hardware • Firmware defined • Serial or parallel interface to commercial USB device • No dedicated global reset • Define logic reset lines in firmware • Utilize JTAG for device reprogramming

Prototype firmware • Tested on current (Los Alamos) board • Jet finder implementation tested • 3 jet finders with inter FPGA communication • Test data loaded into block RAMs • USB interface to PC utilized • Labview application for stimulus and response • Results • Jet finder operates as planned • Inter chip communications robust • Initial device size estimate improper • 100% utilization in XC2V4000 • Speed grade estimate very close • Margin in the single nanosecond range with -6 parts

SERDES testing • Xilinx Simulation model used • Transceiver properly instantiated • Initialization and loopback verified • Standard templates created • Allow easier design and maintenance • De-skew approach successfully simulated • Block RAM based • Doubled as “snapshot” monitor buffer

Signal Counts • Communication with jet finder neighbors @ 40MHz DDR differential • Pre-clustered jets • 16 bits per jet • 10 bit Et, 1 bit ovf, 1 bit tau_veto, 4 bits eta • Up to 6 pre-clustered jets per jet finder • Total: 48 pairs • Jet finder outputs to wheel @ 40 MHz DDR SE • Finished jets • 18 bits per jet • 10 bit Et, 1 bit ovf, 1 bit tau_veto, 4bits eta, 1 bit phi • 1 spare • Up to 6 finished jets per jet finder • Total: 54 pins • Unfinished jets @ 40MHz DDR SE • 14 bits sent directly to wheel/concentrator • 10 bit Et, 1 bit ovf, 1 bit tau_veto, 1 bit phi • 1 spare • Total: 7 pins

Signal counts • Internal communication @ 40MHz DDR SE • Jet summary • 12 bit Et, 1 bit ovf, 1 spare • Missing Et • 16 bit Ex, 16 bit Ey, 1 bit ovf, 1 spare • Total: 24 pins • Summary outputs to wheel @ 40MHz DDR SE • Jet summary • 12 bit Et, 1 bit ovf, 1 spare • Missing Et • 16 bit Ex, 16 bit Ey, 1 bit ovf, 1 spare • Total: 24 pins

Signal counts • Clock • 2 differential pairs • 2 single ended, LVCMOS 2.5V • Slow control, TBD speed and type • Serial read/write, 2 signals • 1 reset • Readout @ 40MHz DDR SE • 8 bits data, 2 control • Data rate: 13.2 Mbyte/second • 3 RCT crates * 22 regions * 2 bytes/region @ 100KHz

Testing • Stand alone operation possible • Requires special test firmware and software • Extension to current labview based test routines possible • Loaded via local JTAG header • USB interface to PC • Loopback of differential interface • Uses the same cable as in operation • FPGA loopback intrinsic • SERDES loopback supported • Source card required for optical testing • Software/firmware requirements not fully defined