The GCT Status

410 likes | 594 Vues

The GCT Status. C. Foudas 1 , Jim Brooke 3 , Magnus Hansen 2 , Greg Heath 3 , Matthew Stettler 2 , Greg Iles 2 , J. Jones 1 , Andrew Rose 1 1 Imperial College, London, UK, 2 CERN Electronics group, 3 Univ. of Bristol. New GCT project started on the 1.2.06

The GCT Status

E N D

Presentation Transcript

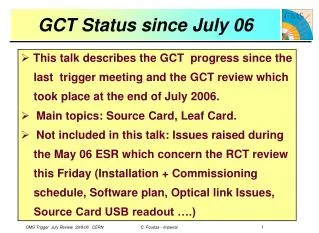

The GCT Status C. Foudas1, Jim Brooke3, Magnus Hansen2 , Greg Heath3, Matthew Stettler2, Greg Iles2, J. Jones1, Andrew Rose1 1Imperial College, London, UK, 2CERN Electronics group, 3Univ. of Bristol • New GCT project started on the 1.2.06 • The design requirements for GCT as set in the Trigger TDR are: • I. Electron/ triggers: Sort the e/ candidates from RCT II. Jet Triggers: Central, Tau and Forward jet finding and sorting. III. Jet Counters: Count Jets in 12 different regions of the detector. IV. Total Transverse, Total Missing Transverse and Total Jet Transverse Energy Calculation V. Receive the Muon data and send them to the GMT. VI. Luminosity Monitoring VII. Readout all the the RCT and GCT data for every L1A. • The new design was required to be self-testing and support data monitoring. • Conservative Design ‘directly derivative of functioning hardware’……. GCT Status, C. Foudas, Imperial College, London

GCT Design: Challenges • Must receive and process the entire RCT output. The GCT algorithms require that all the data are available at some point before the calculation is complete. Hence a way need to be found that concentrates the RCT data in one place to work on them by taking advantage of large FPGA parts. Convert the RCT data to Optical. • The GCT has been assigned a number of different tasks yet we want to avoid having different hardware or firmware implementations for each different task Leaf Card + Staged Commissioning (e/, Jet, ) • Jet Trigger imposes stringent requirements for data sharing. Daisy chain Leaf Cards to do the job • No time to develop anything new from scratch Use existing hardware along with the people that designed them. Leaf Card (M. Stettler) I-DAQ Card (G. Iles, J. Jones) GCT Status, C. Foudas, Imperial College, London

High Level Design Concentrator Card (1/1) Leaf Card (1/8) Wheel Card (1/2) GCT Status, C. Foudas, Imperial College, London

The New GCT Optical Input • The RCT crate output cables are received by three Source Cards. • Each Source Card receives the 2 68 pin80 MHz ECL cables from the RCT crate and converts the signals from copper to optical. GCT Status, C. Foudas, Imperial College, London

RCT to GCT Bandwidth Mapped to: 3 Fibres ×1.6 Gbps 1 Fibres ×1.6 Gbps 2 Fibres ×1.6 Gbps GCT Status, C. Foudas, Imperial College, London

Fibre to RCT Cable Assignments • 3 Electron, 1 muon and 8 ‘Jet’ fibres from each RCT crate GCT Status, C. Foudas, Imperial College, London

Optical Transmitter-Receiver • AFBR-742B 12 Channel Receivers (Leaf) • The HFBR-5720 optical transceiver • can serves one channel at 2.125 Gb/s • It uses an 850 nm VCSEL • 3.3 Volt compatible; LVTTL controlled • Pluggable • Multi Mode 50 m - 125 m • Specified for 50 m transmission. • Each Source card will use four of these transmitters to transmit • the data from two RCT cables. Hence, 3 Source Cards are needed • per RCT crate. • OPTICAL COMPONETS UNDER ORDER (~10/3/06) GCT Status, C. Foudas, Imperial College, London

4 7 4 2 8 3 6 5 The Source Card(John Jones + Andre Rose) • 10-layer 6U VME form factor • USB 2.0 (Cypress SX2) • TTCrx & QPLL • 2xVHDCI SCSI for RCT input • 4 x Optical SFP output & SERDES • TLK2501 & Agilent HFBR-5720AL • LT1963 low-noise analogue supplies • SERDES driver, QPLL & SFPs • PTH05050 switch-mode supplies • Digital logic, FPGA core & aux • XC3S1000-5FG676C GCT Status, C. Foudas, Imperial College, London

Source Card Functionality • Receives the data from two RCT cables (80 MHz ECL) converts them to TTL and transmits them to GCT using 4 optical transmitters. • Receives Clock and commands from the TTC via TTC-Rx • Tests Synchronization by comparing BC0 from TTC and RCT • Generates tests patterns for GCT to self test • Captures 1024 crossing of RCT data under TTC control. • USB readout interface; Readout rate > 28 MB/sec • 3 per RCT crate; 54 needed; plan to build 60 • Derived from the IC I-DAQ design: GCT Status, C. Foudas, Imperial College, London

Source Card Latency RCT->Leaf (Maximum Limit) • Madison Cable (quoted from datasheet) • 1.5ns/ft • Assume 5ft max. length => 1.5x5 = 7.5ns delay • ECL Buffers • 2.5ns-6ns (4ns typical) • FPGA (XC3S1000) • 8ns (synthesised) • SerDes • 38 bit-times 1.6GHz (625ps) = 23.75ns • PCB Tracking • Assume 5-inch@300ps/inch = 1.5ns • Optical Fibre (20m) • 100ns • Estimated Total: • 7.5+4+8+23.75+1.5 = ~1.79BX (board & RCT cable) + 4BX (fibre) GCT Status, C. Foudas, Imperial College, London

Board Testing Plan • Power-Up Testing of Power Supplies • Modular design of power system makes this simple • Power Plane Short Testing • Manual / automatic process, takes ~5 mins • JTAG Testing • Script can be developed at Imperial (done for previous boards) • Script can be sent to assembly company for automated checking • Functionality Testing • Full testing can only be achieved by loading the FPGAs/CPLDs • Aim to generate a test firmware • Loop back TX/RX on optical links, ECL drive buffers using a test card • Source card can be fully ‘internally’ tested GCT Status, C. Foudas, Imperial College, London

Functionality Testing • Software • C++ based via USB 2.0 link • Tested successfully in current project (IDAQ) @ 28MB/s • in two days continuous operation (Beam Test) • Firmware • USB firmware complete • Functionality-testing firmware will be developed in parallel with layout and finished after submission of design to manufacture • Drive optical links with psuedo-random, A-5, ramp, pseudo-RCT • Qualify link BER to <10-12 at 2Gbit/s before use with leaf cards GCT Status, C. Foudas, Imperial College, London

Source Card Schedule • Schematic (1-2 months) • Finished • Layout (2 months) • 2 weeks to go from 15/3/06 • Parts (2 months, long lead parts secured) • Critical parts ordered since end of January • Aim to get prototype parts by submission date • Firmware (2 months) • J. Jones & A. Rose • USB software & firmware already written • Major component left is clocking / calibration firmware for data path GCT Status, C. Foudas, Imperial College, London

Source Card Lay-out Status • Lay out should be complete in 2 weeks GCT Status, C. Foudas, Imperial College, London

Source Card Resource Loaded Schedule • Passed Internal Review on the 1/3/06 • Currently things proceed as planned and according to schedule GCT Status, C. Foudas, Imperial College, London

The Leaf Card Input Links • First Version exists equipped with two VIRTEX-II 4000 parts • Copper input links. • The Final version will have 2 VIRTEX-II Pro parts and Optical Receivers. • USB Interface to read out data for bench tests VIRTEX-II USB Interface for Readout on the Bench GCT Status, C. Foudas, Imperial College, London

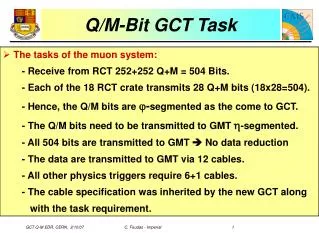

Leaf Card Functionality • Data input: 3 Modes (Jet, Electron, Muon) • Accepts data from 3 RCT crates (Jet) • 32 serial links at 1.6Gbps • 24 for jet data • Shares data with neighboring leaf • Data flows in one direction • LVDS communication with standard cable (Samtec) • Accepts data from 9/18 RCT crates (Electron/muon) • No sharing required for Electrons • Processing • Two Xilinx Virtex2Pro P70 FPGAs • Virtex4FX devices not available yet • XC2VP70FF1513C • Three jet finders total GCT Status, C. Foudas, Imperial College, London

12 channel optical links 1.6Gbps links 12 links 4 links 4 links 12 links 120 pin LVDS link (60 pairs) 120 pin LVDS link (60 pairs) 4 links unused XC2VP70FF1513C XC2VP701513C Pre-clustered jets: 96 pins (48 pairs) 200 pins Pre-clustered jets: 96 pins (48 pairs) Et summary: 24 pins Readout: 10 pins Misc: 20 pins Finished jets: 54 pins Unfinished jets: 7 pins Finished jets: 54 pins Unfinished jets: 7 pins Energy summary: 24 pins Clock and control: 14 pins Readout: 20 pins Finished jets: 54 pins Unfinished jets: 7 pins P13 P11 P23 P21 P14 P12 P24 P22 The Leaf Card Block Diagram (Matt Stettler) GCT Status, C. Foudas, Imperial College, London

Jet Finder Progress Since 31/1/06 - I • The Current Leaf Card has tested by Matt and found to be working for data transfers speeds which is much higher than required for the Jet finder needs (40 MHz). • We are confident that this board can host the TDR Jet algorithms and the Virtex-II Pro P70 gives us a comfortable 40% contingency in FPGA capacity and enough margin in speed. • Latency: 4 CC (SERDES) + 11 CC (JET) • Schematic Capture finished: • Currently the board is under lay-out at Los Alamos: • Delivery date is 1.07.06: Again at the moment on schedule • The contract with Los Alamos should be signed within a week • The Jet finder firmware is now finished (Magnus) and has been up-loaded to the Virtex-II 4000 part (equivalent to the Virtex-II Pro P50 that we originaly planned to have on the Leaf):Regional Energy data have been injected at the Leaf card via USB and Jets come out as expected Jet-finder works GCT Status, C. Foudas, Imperial College, London

Testing Plan • Stand alone operation possible • USB adaptor from current board • Operational now • Used in conjunction with bench top supply • LabView test interface operational • Currently in use for jet finder algorithm development • New USB adaptor ready for fabrication • Includes power supply and loopback • Interface to PC on bench top supply • Cable loopback for board to board link • Uses production cable (straight through) • MGTs tested through internal loopback • Full test requires front end card • Front end card contains pattern generator for link verification GCT Status, C. Foudas, Imperial College, London

Risk Assessment • Based on working design • Basic layout retained • Power supplies, decoupling layout • Plane structure • New elements • Many more high speed serial links • 32 instead of 8 • Congestion and signal integrity will be an issue • Optical interfaces • Used elsewhere in CMS • New FPGA package • FF1517 requires some modifications to decoupling cap layout • Risk defined by link density rather than speed • Serial links run at 1.6GBps • One half rated performance • Existing design tested to 2.5 GBps • Algorithm tests in current board define FPGA logic requirement • 30% headroom (2M gates/chip) at this point with no logic sharing GCT Status, C. Foudas, Imperial College, London

Leaf Card Resource Loaded Schedule GCT Status, C. Foudas, Imperial College, London

Leaf Card Latest News: • 8/3/06: Passed internal Review; Decisions: • Data capture and test pattern injection to GCT and GT will implemented at the Leaf Card inputs. • Data error monitor will implemented via CRC during the gaps. • Possible changes to the power. • Integration plan with the leaf for synchronous data transfers discussed and preliminary plan developed. • Monthly reports from LANL agreed • Design review with LANL group at CERN late in May 06 before launching production. GCT Status, C. Foudas, Imperial College, London

The Wheel CardM. Stettler • 9U VME card (but only VME power is used) • Supports 3 Leaf Cards and compresses their data before sending them to the Concentrator Card • Leaf Wheel and Concentrator Cards communicate via parallel 40 MHz DDR/QDR point to point LVDS connections. • Uses to VIRTEX-4 LX parts to receive the Jet data and do the pre-sorting. • J1,J2,J3 are connectors for flat cables to communicate with the Concentrator Card GCT Status, C. Foudas, Imperial College, London

Wheel Card Functionality • Carries 3 leaf cards • Compresses (sorts) Jet data • Calculates Et and Jet count • Single ended electrical interface • Interfaces to concentrator board • High speed cable interface • LVDS electrical interface • 9U VME form factor • 3 CC Latency GCT Status, C. Foudas, Imperial College, London

Wheel Card Implementation • Data Input • Accepts data from 3 leaf cards • Nearly 600 signals, single ended • Passes through unfinished Jet data • Outputs sorted jet, jet count and Et • Roughly 200 signals to Concentrator • Processing • Two Xilinx Virtex4 FPGAs • XC4VLX100FF1513 • I/O (as opposed to logic) intensive design • Advanced Virtex4 I/O features reduce risk • Better double/quad data rate support • Improved Differential support • One for Jet sorting, one for Et and Jet count GCT Status, C. Foudas, Imperial College, London

Test and Verification • Stand alone operation possible • USB adaptor ready for fabrication • Modification of leaf card test board • Includes power supply and loopback • Used in conjunction with bench top supply • LabView test interface operational with leaf card • Cable loopback for concentrator link • Uses production cable (straight through) • Board fully testable • USB adaptor and loopback verify all signals GCT Status, C. Foudas, Imperial College, London

Risk Assessment • Virtex4 FPGAs • New devices • Highly desirable due to enhanced I/O • Improved speed and density • Conservative design requirements • May require .0201 decoupling cap scheme • Blind/buried vias, small drill diameters • .008” used extensively on leaf card • No high speed I/O requirements • No SERDES links • 40 MHz single ended possible to leaf cards • 40MHz DDR differential to concentrator • Considerable enhancement potential built in • Straightforward, but physically large design • Relies on typical, rather than best case performance • No time critical design elements relative to FPGA specs GCT Status, C. Foudas, Imperial College, London

Wheel Status: M. Stettler • The Wheel card schematic capture has been finished: • The Card is under lay out at CERN earlier than we originally thought (Schedule adjusted for this) • Wednesday 15/3/06 the Wheel card will undergo through internal review. GCT Status, C. Foudas, Imperial College, London

Wheel Card: Resource Loaded Schedule • Schedule Consistent with delivery of GCT in July 07 GCT Status, C. Foudas, Imperial College, London

The Concentrator Card Lay-OutGreg Iles Leaf Card (one on each side) VME Wheel Connectors Wheel Connectors GT Links S-LINK64 TTC Interface GCT Status, C. Foudas, Imperial College, London

Implementation • Data Input • Accepts data from 2 leaf cards electrons and two wheel cards • Nearly 400 signals, differential • Outputs highest ranking jets, jet count and Et • 7, 1.6GBps links to GT • Processing • Two Xilinx Virtex4 FPGAs • XC4VLX100FF1513 • I/O (as opposed to logic) intensive design • Advanced Virtex4 I/O features reduce risk • Better double/quad data rate support • Improved Differential support • One for Jet sorting, one for Et electron, and Jet count • Also S-link and timing (TTC) functions • Latency 8 Clock Counts GCT Status, C. Foudas, Imperial College, London

Testing • Stand alone operation possible • USB adaptor ready for fabrication • Same module as wheel card • Modification of leaf card test board • Includes power supply and loopback • Used in conjunction with bench top supply • LabView test interface operational with leaf card • Cable loopback for wheel link • Uses production cable (straight through) • SERDES reciever allows loopback • Links to GT fully testable • Board fully testable • USB adaptor and loopback verify all signals • Assume a crate with VME controller available • Just needed for VME interface GCT Status, C. Foudas, Imperial College, London

Status • Schematic capture under way and on schedule • Internal Review on Wednesday 22/5/06 • Very critical Card whose schedule sets the overall schedule GCT Status, C. Foudas, Imperial College, London

Concentrator Card:Resource Loaded Schedule GCT Status, C. Foudas, Imperial College, London

Muons Jets <0 Jets >0 Electrons Commission it in Stages GCT Status, C. Foudas, Imperial College, London

Milestones I Milestone GCT-1 : Integration of Prototype Source Card + Prototype Leaf Card End byAugust 06. Milestone GCT-1 : Integration1 Source+ 1 Leaf+ 1 Concentrator Start in October 06 Milestone GCT-3: Commissioning of the Electron Triggers (RCT+GCT+GT). January 07 Milestone GCT-4: Commissioning of the Jet Triggers July 07 GCT Status, C. Foudas, Imperial College, London

Schedule Overview I GCT Status, C. Foudas, Imperial College, London

Schedule Overview II GCT Status, C. Foudas, Imperial College, London

Schedule Overview III GCT Status, C. Foudas, Imperial College, London

Conclusions and Outlook • There has been a lot of activity over the past two months both in terms of design and in terms of planning. • 3 out 4 cards are finished with schematic capture and are now on lay out. • Internal reviews are necessary and have been happening over the past month and will continue with Wheel (tomorrow) and Concentrator card (in a week) • We are trying to get the software project Launched for the GCT and Jim should have it very soon. It should be organized in the same details as the hardware one (both because it is needed plus because it has been requested) • This system can be delivered by early-mid 07. • Crucial milestone this July when the Leaf comes back and and must be integrated with the Source which by then should be finished GCT Status, C. Foudas, Imperial College, London