PICo Arithmetic and Logic Unit

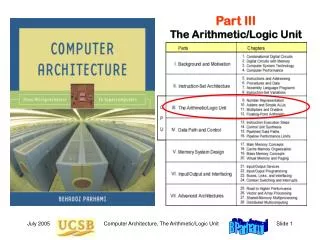

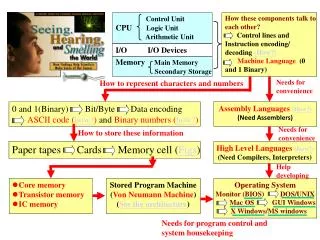

PICo Arithmetic and Logic Unit. The Need for Speed (with minimal area and power). ALU Top Level Topology. Six primary logic blocks Shift, Add, Compare, And, Or, OutMux Pass A Direct to Out Shift Topology Array of muxes Critical Path Add->Compare->MUX. Metrics. Adder Block.

PICo Arithmetic and Logic Unit

E N D

Presentation Transcript

PICo Arithmetic and Logic Unit The Need for Speed (with minimal area and power)

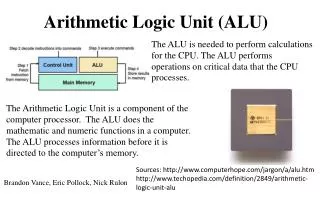

ALU Top Level Topology • Six primary logic blocks • Shift, Add, Compare, And, Or, OutMux • Pass A Direct to Out • Shift Topology • Array of muxes • Critical Path • Add->Compare->MUX

Adder Block • Mirror Adder used as the individual full adder • Carry-select topology • Variable block sizes of 6-4-3-2-1 for O(N^0.5) delay growth.

Subtraction (The Adder Extended) • Utilizes the adder to implement two’s complement subtraction • Cin= 1 and B inverted • With these conditions selected by a mux based on the sub op code the add becomes two’s complement • Minimizes Area and power (only one structure)

Arbitrary Function: Comparator • Three Scenarios • Signified by three most significant bit output • 0:13 grounded • 16bit XOR and 16bit NAND • Determines if A==B • Subtract Utilized • Two’s complement output of ADD block compares A and B • Drawbacks • Area and extra NAND delay on critical path

MUX Topology 2 to 1 MUX Pass Gate Schematic 8 to 1 MUX built from 2 to 1 MUXs

Optimization • Sized the mirror adder according to logical effort, as shown in the textbook • Minimum sized all the other functions as they are not the worst case path • Buffered all the long (>3) transmission gate paths for more speed.

Registers • Pair of muxes with feedback and buffered Q.