Built-In Self-Test

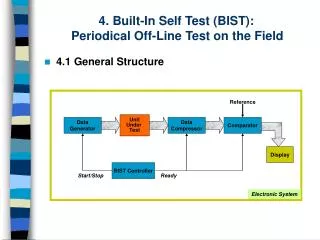

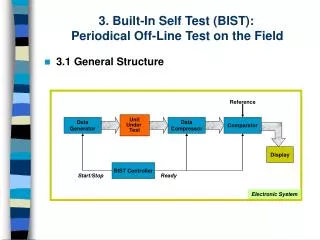

Built-In Self-Test. Built-in Self Test (BIST). Basics Test Pattern Generators Response Analyzers BIST Examples BIST of PLAs. BIST. BIST - General Organization. Test Generator. Circuit Under Test (CUT). Response Compressor. BIST Basics. BIST - Goal.

Built-In Self-Test

E N D

Presentation Transcript

Built-in Self Test (BIST) • Basics • Test Pattern Generators • Response Analyzers • BIST Examples • BIST of PLAs BIST

BIST - General Organization Test Generator Circuit Under Test (CUT) Response Compressor BIST Basics

BIST - Goal • Reduce input/output pin signal traffic. • Permit easy circuit initialization and observation. • Eliminate as much test pattern generation as possible. • Achieve fair fault coverages on general class of failure mode. • Reduce test time. • Execute at-speed testing. • Test circuit during burn-in. BIST Basics

BIST Issues • Area overhead • Performance degradation • Fault coverage • Ease of Implementation • Capability for system test • Diagnosis capability BIST Basics

BIST Techniques • Stored Vector Based • Microinstruction support • Stored in ROM • Algorithmic Hardware Test Pattern Generators • Counter • Linear Feedback Shift Register • Cellura Automata BIST Basics - LFSR

Linear Feedback Shift Register Type 1 Type 2 • Unit delay - D Flip flop • Modulo 2 adder - XOR gate • Modulo 2 multiplier -connection + D1 D2 D3 D4 D1 D2 D3 D4 + BIST Basics - LFSR

LFSR - Why? • Simple and Regular Structure • Compatible with scan DFT design • Capable of exhaustive and/or pseudo exhaustive testing • Low aliasing probability BIST Basics - LFSR

n i å g ( x ) = g x i i = 0 LFSR - Recurrence Relation ... + + + • Generating Function • Characteristic polynomial g1 g2 gn-1 D1 D2 D3 Dn-1 Dn ... Is a-1 a-2 a-3 ... a-n+1 a-n Cs am-1 am-2 am-3 ... am-n+1 am-n BIST Basics - LFSR

LFSR - Recurrence Relation (continue) n am= å gi am-i i =1 ¥ G(x) = å am xm = å ågi am-i xm = ågi xiå am-i xm-i = å gi xi[a-i x -i +...+ a-1 x -1 + åam xm] = å gi xi[a-i x -i +...+ a-1 x -1 + G(x)] m=0 n n ¥ ¥ m=0 i =1 i =1 m=0 n ¥ i =1 m=0 n i =1 BIST Basics - LFSR

LFSR - Recurrence Relation (continue) G(x)is function of initial state and g(x) BIST Basics - LFSR

LFSR Example 1 0 0 0 0 0 0 1 0 0 1 1 0 1 1 1 1 1 1 1 1 1 1 0 1 1 0 1 1 0 1 0 0 1 0 1 1 0 1 1 0 1 1 0 1 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 0 + D2 D3 D4 D1 BIST Basics - LFSR

LFSR - Definitions • If the sequence generated by an n-stage LFSR has period 2n-1, then it is called a maximum-length sequence. • The characteristic polynomial associated with maximum-length sequence is called a primitive polynomial. • An irreducible polynomial is one that cannot be factored; i.e., it is not divisible by any other polynomial other than 1 and itself. BIST Basics - LFSR

LFSR - Theories • If the initial state of an LFSR is a-1=a-2=...=a1-n=0, a-n=1, then the LFSR sequence {am} is periodic with a period that is the smallest integer k for which P(x) divides (1+xk) • An irreducible polynomial P(x) satisfies the following two conditions is a primitive polynomial: • It has an odd number of terms including the 1 term. • If its degree n is greater than 3, then P(x) must divide 1+xk, where k=2n-1 BIST Basics - LFSR

LFSR - Properties • The number of 1s in an m-sequence differs from the number of 0s by one. • An m-sequence produces an equal number of runs of 1s and 0s. • In every m-sequence, one half the runs have length 1, one fourth have length 2, one eighth have length 3, and so forth, as long as the fractions result in integral numbers of runs. BIST Basics - LFSR

LFSR - Properties (continue) • M-sequences generated by LFSRs are called pseudo random sequence. • The autocorrelation of any output bit is very close to zero. • The correlation of any two output bits is very close to zero. BIST Basics - LFSR

input f(x) gn gn-1 gn-2 g1 g0 Dn Dn-1 D2 D1 ... + + + + output h(x) LFSR - Polynomial Multiplication BIST Basics - LFSR

D4 D3 D2 D1 + + Output stream D4D3D2D1 Input stream 0 0 0 0 1 1 0 1 1 1 0 0 1 1 0 1 1 0 1 0 1 1 0 1 1 0 1 0 1 1 0 1 1 0 1 1 0 1 0 1 x7 x5 x4 x2 1 LFSR - Polynomial Multiplication BIST Basics - LFSR

LFSR - Polynomial Division g0 g1 gn-2 gn-1 gn D1 D2 Dn-1 Dn ... + + + + input output BIST Basics - LFSR

LFSR - Polynomial Division (example) Input 011011011 Q(x) Output 11001 D1 D2 D3 D4 M(x) + + 1+x+x4 x+x2+x4+x5+x7+x8 M(x) D3D2D1D0Q(x) 0 1 1 0 1 1 0 1 1 0 0 0 0 0 1 1 0 1 1 0 1 1 0 1 1 0 0 1 0 0 1 0 1 1 0 0 1 0 0 1 0 1 1 0 0 1 0 0 1 0 0 1 0 1 1 0 0 1 1 0 1 1 1 1 0 0 1 after 4 shifts 1 +x2+x3 1 +x +x4 (x8+x7+x5+x4+x2+x) ¸ (x4+x3+1) = x4+x+1 R(x) = x3+x2+1 BIST Basics - LFSR

LFSR - Summary • LFSRs have two types. • LFSRs can implement polynomial division and multiplication in GF(2). • As polynomial multipliers, LFSRs are capable of generating random vector. • As polynomial divisors, LFSRs are capable of compressing test responses. BIST Basics - LFSR

Cellura Automata (CA) • A One-Dimensional Array of Cells. • Each cell contains a storage device and next state logic. • Next state is a function of current state of the cell and its neighboring cells. Next State Next State Next State D Q D Q D Q Three-Cell Neighbor -- von Newmann Neighborhood BIST Basics - CA

State A0 A1 A2 A3 A4 A5 A6 A7 Ci+1 Ci Ci-1 Next State KMap FCA A0 A2 A4 A6 A1 A3 A5 A7 CiCi-1 00 01 11 10 Ci+1 0 1 0 1 0 Cellura Automata - Name • Name of CA Functions is determined by its truth table. 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 (defined by Wolfram) Example: Name = 64+32+4+2 = 102 1 0 1 0 1 BIST Basics - CA

0 0 Fca Fca Fca Fca Fca Fca D Q D Q D Q D Q D Q D Q Cellura Automata - Hardware CA with Null Boundary Condition Standard - All the CAs are of the same type Hybrid - The CAs are of different type BIST Basics - CA

Fca Fca Fca D Q D Q D Q Cellura Automata - Hardware CA with cyclic Boundary Condition Fca Fca Fca D Q D Q D Q BIST Basics - CA

PG Hardware Stored Patterns Counter Based LFSR Based Cellura Automata Pattern Generated Deterministic Pseudorandom Exhaustive Pseudo exhaustive BIST - Pattern Generation BIST - TestGen

TG - Stored Pattern • Functional Chip Tests • Test for structured logic such as ILA • Supplemental test for uncovered faults • Test control for other methods • Architecture support self test command BIST - TestGen - Stored Pattern

hard to detect fault Stored Pattern- Supplement for Uncovered faults • Hard-to-detect faults not covered by random testing BIST - TestGen - Stored Pattern

Walking Sequence Counting Sequence 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 TG - Counter Based • Generates regular test sequences such as walking sequences and counting sequences for memory and interconnect testing BIST - TestGen - Counter Based

TG - LFSR • Exhaustive Testing • Pseudoexhaustive Testing • Pseudorandom Testing • Weighted Pseudorandom Testing BIST - TestGen - LFSR

LFSR CUT SA TG - Exhaustive Testing • Apply all possible input combinations • A complete functional testing • 100% coverage on all possible faults • Testing time and hardware overhead are the major considerations for circuits with large number of inputs. BIST - TestGen - LFSR

BIST - Pseudo-exhaustive Testing (PET) • Apply all possible input combination to every partitioned subcircuits. • 100% faults coverage on single faults and multiple faults within the subcircuit. • Testing time is determined by the number of subcircuits and the number of inputs to the subcircuit. • Partitioning is a difficult task.

L F S R MUX Subcircuit under test S A TG - PET Hardware Example normal inputs CUT BIST - TestGen - LFSR

BIST - Pseudo Random Testing • Apply random test sequence generated by LFSR/CA. • Simplest to design and implement • Lowest in hardware overhead • Fault coverage is a function of the test length and the testability of the circuits BIST - TestGen - LFSR

Combinational Sequential LFSR LFSR Combinational circuit Combinational circuit SA SA BIST - Pseudo Random Testing Hardware (BEST) (Circular BIST) BIST - TestGen - LFSR

BIST - Pseudo Random Testing Hardware LFSR Shift register LFSR Circuit Under Test S R S R S R CUT CUT SA SA (CEBT) (STUMPS) BIST - TestGen - LFSR

Pseudo Random Test Length • eth: Escape Threshold • gmin: the detection probability of the hardest to detect fault by a random vector • k: the number of faults with detection probability 2gmin • Example 1: eth=0.001, gmin=1E-5, k=5 * m=851,716 • Example 2: eth=0.001, gmin=1E-5, k=50 * m=1,081,973 BIST - TestGen - LFSR

LFSR 0 0 123 193 61 114 228 92 25 D Q D Q D Q D Q D Q D Q D Q 1/8 3/4 1/2 7/8 1/2 0.8 0.6 0.8 0.4 0.5 0.3 0.3 BIST - Weighted Pseudo Random Test LFSR Based Weighted Celluar Automaton BIST - TestGen - LFSR

BIST - Response Compression • Introduction • Ones-Count Compression • Transition-Count Compression • Syndrome-Count Compression • Signature Analysis • Space Compression BIST - ResComp

BIST - Response Compression • Bit-to-bit Comparison is infeasible for BIST. • Compress a very long output sequence into a single signature. • Compare the compressed word with the prestored gold signature to determine the correctness of the circuit. • Many output sequences may have the same signature after the compression, the aliasing problem. • Poor diagnosis resolution after compression. BIST - ResComp

CUT TestPattern Clock Counter Ones-Count - Hardware • Apply predetermined patterns • Count the number of ones in the output sequence. BIST - ResComp

Ones Counter - Aliasing • Aliasing Probabilitym: the test lengthr: the number of ones • r=m/2, the case with the highest aliasing probability • r=m and r=0, no aliasing probability • For combinational circuits, the input sequence can be permuted without changing the count. BIST - ResComp

DFF CUT TestPattern Clock Counter Transition Count • Apply predetermined patterns • Count the number of the transitions(0 *1 and 1 *0) BIST - ResComp

Transition Count • Aliasing Probabilitym: the test lengthr: the number of transitions • r=m/2, highest aliasing probability. r=0 and r=m , no aliasing probability • For combinational circuits, the input sequence cannot be permuted. • One can reorder the test sequence to minimize the aliasing probability. BIST - ResComp

CUT random test pattern Clock Syndrome counter Counter / Syndrome Syndrome Testing • Apply random patterns. • Count the probability of 1. • The property is similar to that of ones count. BIST - ResComp

Signature Analysis • Apply predetermined test patterns. • Divide the Output Sequence by LFSR. CUT Test Pattern LFSR BIST - ResComp

Signature Analysis • Aliasing Probabilitym: test length, n: length of LFSR • Aliasing probability is output independent. • An LFSR with two or more nonzero coefficient detect any single faults. • An LFSR with primitive polynomial detect any double faults separated less than 2n-1 • An LFSR with g0=1 detects all burst error of length less than n. BIST - ResComp

D4 D3 D2 D1 + + + + + type 1 D4 D3 D2 D1 + + + + type 2 Multiple Input Signature Register (MISR) BIST - ResComp

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 + + + + + + + + + + + + + + + + + + + + + + + + + + P1 P2 P3 P4 P5 Space Compression • Use space compression to handle large output circuits. • Use XOR gates to compress space. • Use Error Control Coding to achieve better fault coverage. • Example: A 16 SEC-DED code compresses 16 outputs into 5. BIST - ResComp

CUT TC CUT TC SC SC BIST - Space and Time Compression Space-Time Compression Time-Space Compression BIST - ResComp