L9 : Low Power DSP

L9 : Low Power DSP. Jun-Dong Cho SungKyunKwan Univ. Dept. of ECE, Vada Lab. http://vada.skku.ac.kr. Low Power DSP. 수행시간의 대부분이 DO-LOOP 에서 이루어짐. VSELP Vocoder : 83.4 % 2D 8x8 DCT : 98.3 % LPC computation : 98.0 %. DO-LOOP 의 Power Minimization ==> DSP 의 Power Minimization.

L9 : Low Power DSP

E N D

Presentation Transcript

L9 : Low Power DSP Jun-Dong Cho SungKyunKwan Univ. Dept. of ECE, Vada Lab. http://vada.skku.ac.kr

Low Power DSP • 수행시간의 대부분이 DO-LOOP에서 이루어짐 • VSELP Vocoder : 83.4 % • 2D 8x8 DCT : 98.3 % • LPC computation : 98.0 % DO-LOOP의 Power Minimization ==> DSP의 Power Minimization VSELP : Vector Sum Excited Linear Prediction LPC : Linear Prediction Coding

VLSI Signal Processing Design Methodology • pipelining, parallel processing, retiming, folding, unfolding, look-ahead, relaxed look-ahead, and approximate filtering • bit-serial, bit-parallel and digit-serial architectures, carry save architecture • redundant and residue systems • Viterbi decoder, motion compensation, 2D-filtering, and data transmission systems

Loop unrolling • The technique of loop unrolling replicates the body of a loop some number of times (unrolling factor u) and then iterates by step u instead of step 1. This transformation reduces the loop overhead, increases the instruction parallelism and improves register, data cache or TLB locality.

Loop Unrolling Effects • Loop overhead is cut in half because two iterations are performed in each iteration. • If array elements are assigned to registers, register locality is improved because A(i) and A(i +1) are used twice in the loop body. • Instruction parallelism is increased because the second assignment can be performed while the results of the rst are being stored and the loop variables are being updated.

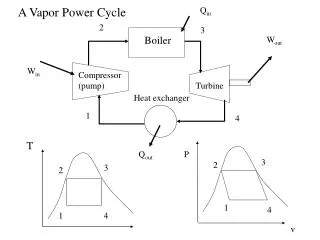

Loop Unrolling (IIR filter example) loop unrolling : localize the data to reduce the activity of the inputs of the functional units or two output samples are computed in parallel based on two input samples. Neither the capacitance switched nor the voltage is altered. However, loop unrolling enables several other transformations (distributivity, constant propagation, and pipelining). After distributivity and constant propagation, The transformation yields critical path of 3, thus voltage can be dropped.

DFG after Loop Unrolling The estimated power-consumption reduction is now: obtaining a reduction of 9.4%.

Switching Activity Reduction (a) Average activity in a multiplier as a function of the constant value (b) A parallel and serial implementations of an adder tree.

FIR Parallelization Mahesh Mejendale, Sunil D. Sherlekar, G. Venkatesh “Low-Power Realization of FIR Filters on Programmable DSP’s” IEEE Transations on very large scale integration (VLSI) system, Vol. 6, No. 4, December 1998

Data- flow based transformations • Tree Height reduction. • Constant and variable propagation. • Common subexpression elimination. • Code motion • Dead-code elimination • The application of algebraic laws such as commutability, distributivity and associativity. • Most of the parallelism in an algorithm is embodied in the loops. • Loop jamming, partial and complete loop unrolling, strength reduction and loop retiming and software pipelining. • Retiming: maximize the resource utilization.

Tree-height reduction • Example of tree-height reduction using commutativity and associativity • Example of tree-height reduction using distributivity

Sub-expression elimination • Logic expressions: • Performed by logic optimization. • Kernel-based methods. • Arithmetic expressions: • Search isomorphic patterns in the parse trees. • Example: • a= x+ y; b = a+ 1; c = x+ y; • a= x+ y; b = a+ 1; c = a;

Examples of other transformations • Dead-code elimination: • a= x; b = x+ 1; c = 2 * x; • a= x; can be removed if not referenced. • Operator-strength reduction: • a= x2 ; b = 3 * x; • a= x * x; t = x<<1; b = x+ t; • Code motion: • for ( i = 1; i < a * b) { } • t = a * b; for ( i = 1; i < t) { }

Control- flow based transformations • Conditional expansion • Transform conditional into parallel execution with test at the end. • Useful when test depends on late signals. • May preclude hardware sharing. • Always useful for logic expressions. • Example: • y= ab; if ( a) x= b+d; else x= bd; can be expanded to: x= a( b+ d) + a’bd; • y= ab; x= y+ d( a+ b); • Model expansion. • Expand subroutine flatten hierarchy. • Useful to expand scope of other optimization techniques. • Problematic when routine is called more than once. • Example: • x= a+ b; y= a * b; z = foo( x, y) ; • foo( p, q) {t =q-p; return(t);} • By expanding foo: • x= a+ b; y= a * b; z = y-x;

DIGLOG multiplier 1st Iter 2nd Iter 3rd Iter Worst-case error -25% -6% -1.6% Prob. of Error<1% 10% 70% 99.8% With an 8 by 8 multiplier, the exact result can be obtained at a maximum of seven iteration steps (worst case)

Logarithmic Number System --> Significant Strength Reduction